### Extending Intel-x86 Consistency and Persistency: Formalising the Semantics of Intel-x86 Memory Types & Non-temporal Stores

Azalea Raad Imperial College London

NANDA Workshop, 2022

azalea@imperial.ac.uk

SoundAndComplete.org

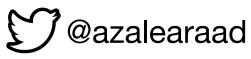

- \* Write *directly to memory*, bypassing cache

- \* Avoids *cache pollution*

- \* Ubiquitous (application-level use)

- \* Write *directly to memory*, bypassing cache

- \* Avoids cache pollution

- Ubiquitous (application-level use)

➡ 332K instances of MOVNTI on GitHub including in C, C++ & Assembly

MOVNTI

( )

place Explore

| Repositories | 0    |

|--------------|------|

| Code         | 308K |

| Commits      | 69К  |

| Issues       | 61   |

| Discussions  | 0    |

| Packages     | 0    |

| Marketplace  | 0    |

| Topics       | 0    |

| Wikis        | 6    |

| Users        | 0    |

| Languages     |         |  |

|---------------|---------|--|

| CSV           | 1,900   |  |

| с             | 102,715 |  |

| Lua           | 5,530   |  |

| Makefile      | 9,001   |  |

| Unix Assembly | 46,848  |  |

| JavaScript    | 11,240  |  |

| Lex           | 490     |  |

| JSON          | 7,353   |  |

| LLVM          | 483     |  |

| HTML          | 585     |  |

| Vim Script    | 6,691   |  |

| Text          | 54,804  |  |

| Assembly      | 420     |  |

| C++           | 27,361  |  |

|               |         |  |

### 308,196 code results Listoffer/Xen-4.1.2 stubdom/newlib-1.16.0/newlib/libc/machine/x86\_64/memset.S /\* Store 128 bytes at a time with minimum cache shrq **\$7, r**cx polution \*/ .p2align 4 loop novnti rax, (rdi) 8 (rdi) ovnti rax, 16 (rdi) ovnti rax, movnti rax, 24 (rdi) movnti rax, 32 (rdi) Unix Assembly Showing the top five matches Last indexed on 2 Apr Listoffer/Xen-4.1.2 stubdom/newlib-1.16.0/newlib/libc/machine/x86\_64/memset.S.bak shrq \$7, rcx /\* Store 128 bytes at a time with minimum cache

|                                            | polution                                                               | */                                                 |                        |                           |           |         |                 |      |        |      |       |       |   |       |

|--------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------|------------------------|---------------------------|-----------|---------|-----------------|------|--------|------|-------|-------|---|-------|

| 40                                         |                                                                        |                                                    |                        |                           |           |         |                 |      |        |      |       |       |   |       |

| 41                                         | .p2alig                                                                | jn 4                                               |                        |                           |           |         |                 |      |        |      |       |       |   |       |

| 42                                         | loop:                                                                  |                                                    |                        |                           |           |         |                 |      |        |      |       |       |   |       |

| 43                                         | movnti                                                                 | rax,                                               |                        | (rdi)                     |           |         |                 |      |        |      |       |       |   |       |

| 44                                         | movnti                                                                 | rax,                                               | 8                      | (rdi)                     |           |         |                 |      |        |      |       |       |   |       |

| 45                                         | movnti                                                                 | rax,                                               | 16                     | (rdi)                     |           |         |                 |      |        |      |       |       |   |       |

| 46                                         | movnti                                                                 | rax,                                               | 24                     | (rdi)                     |           |         |                 |      |        |      |       |       |   |       |

| 47                                         | movnti                                                                 | rax,                                               | 32                     | (rdi)                     |           |         |                 |      |        |      |       |       |   |       |

| Showing                                    | the top five r                                                         | natche                                             | s La                   | ast inde                  | exed on 2 | 2 Apr   |                 |      |        |      |       |       |   |       |

|                                            |                                                                        |                                                    |                        |                           |           |         |                 |      |        |      |       |       |   |       |

|                                            | aozh/Middlew<br>5.0/stubdo                                             |                                                    |                        |                           | )/newli   | b/libc, | 'machi          | ne/> | (86_64 | 1/me | mset. | .S.ba | k |       |

|                                            |                                                                        |                                                    | wlib                   |                           | )/newli   |         | /machi<br>Store |      |        |      |       |       |   | num c |

| xen-4.                                     | 5.0/stubdo                                                             | m/ne<br>\$7,                                       | wlib                   |                           | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.                                     | 5.0/stubdo<br>shrq                                                     | m/ne<br>\$7,                                       | wlib                   |                           | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.                                     | 5.0/stubdo<br>shrq                                                     | m/ne<br>\$7,<br>*/                                 | wlib                   |                           | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.                                     | 5.0/stubdo<br>shrq<br>polution                                         | m/ne<br>\$7,<br>*/                                 | wlib                   |                           | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.                                     | 5.0/stubdo<br>shrq<br>polution<br>.p2alig                              | m/ne<br>\$7,<br>*/<br>yn 4                         | wlib<br>rcx            |                           | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.<br>39<br>40<br>41<br>42             | 5.0/stubdo<br>shrq<br>polution<br>.p2alig<br>loop:                     | m/ne<br>\$7,<br>*/<br>yn 4<br>rax,                 | wlib<br>rcx            | -1.16.(<br>(rdi)          | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.<br>39<br>40<br>41<br>42<br>43       | 5.0/stubdo<br>shrq<br>polution<br>.p2alig<br>loop:<br>movnti           | m/ne<br>\$7,<br>*/<br>jn 4<br>rax,<br>rax,         | wlib<br>rcx<br>8       | -1.16.(<br>(rdi)<br>(rdi) | )/newli   |         |                 |      |        |      |       |       |   | num c |

| xen-4.<br>39<br>40<br>41<br>42<br>43<br>44 | 5.0/stubdo<br>shrq<br>polution<br>.p2alig<br>loop:<br>movnti<br>movnti | m/ne<br>\$7,<br>*/<br>jn 4<br>rax,<br>rax,<br>rax, | wlib<br>rcx<br>8<br>16 | -1.16.(<br>(rdi)<br>(rdi) | )/newli   |         |                 |      |        |      |       |       |   | num c |

- \* Write *directly to memory*, bypassing cache

- \* Avoids cache pollution

- Ubiquitous (application-level use)

- ➡ 332K instances of MOVNTI on GitHub including in C, C++ & Assembly

- memset function in the C runtime

- memcpy in glibc

- \* Write *directly to memory*, bypassing cache

- \* Avoids cache pollution

- Ubiquitous (application-level use)

- ➡ 332K instances of MOVNTI on GitHub including in C, C++ & Assembly

- memset function in the C runtime

- memcpy in glibc

- Large-scale projects: PMDK and SPDK to interface with NVM

- Large-scale projects: DPDK and DML to communicate with accelerators

\* Also known as *memory cacheability*\*: UC, WC, WT, WB

\* There are two other memory types: WP and UC

- \* Also known as *memory cacheability*\*: UC, WC, WT, WB

- \* Non-cacheable types: bypass memory, access (read/write) memory directly

- ➡ UC: Strong Uncacheable

- ➡ WC: Write Combining

- \* Cacheable types: memory accesses go through the cache hierarchy

- ➡ WB: Write Back

- ➡ WT: Write Through

\* There are two other memory types: WP and UC

- \* Also known as *memory cacheability*\*: UC, WC, WT, WB

- \* Non-cacheable types: bypass memory, access (read/write) memory directly

- UC: Strong Uncacheable

- → WC: Write Combining

- \* Cacheable types: memory accesses go through the cache hierarchy

- → WB: Write Back

- → WT: Write Through

- Use within system-level code

- Linux Kernel: WC for frame buffer optimisation

- Linux Kernel: UC for memory-mapped I/O

- Interaction with non-cache-coherent DMA device drivers

\* There are two other memory types: WP and UC

\* There are two other memory types: WP and UC

### Ex86 (Extended x86):

Formal consistency semantics of Intel-x86 architectures including non-temporal stores & memory types

З

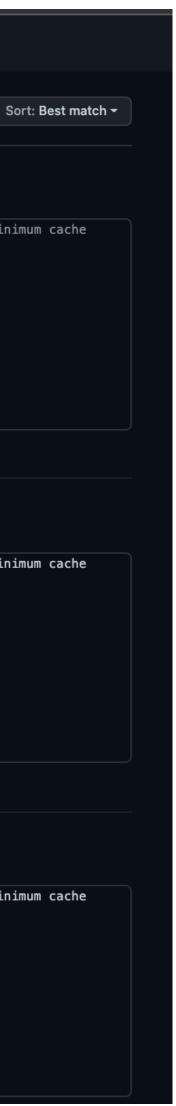

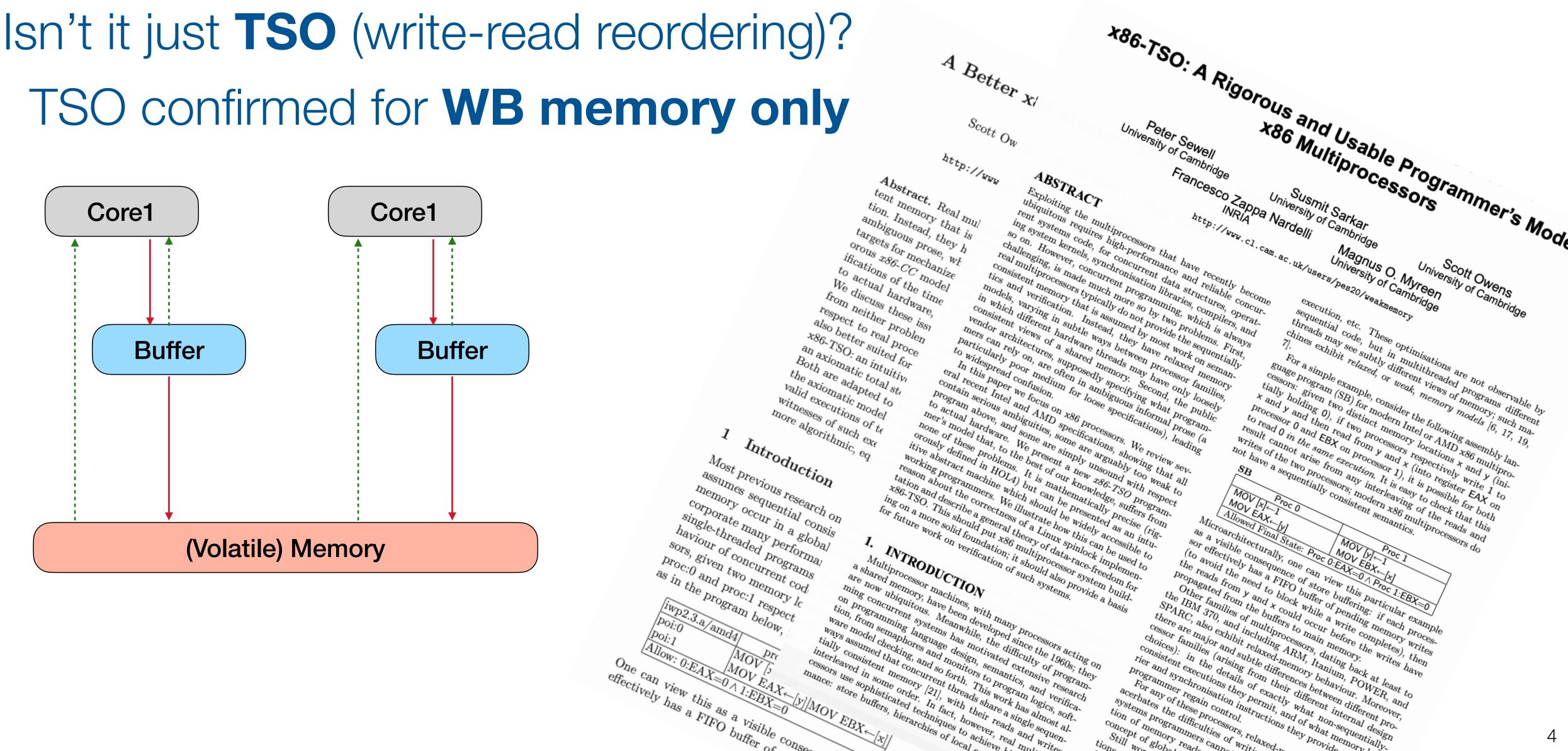

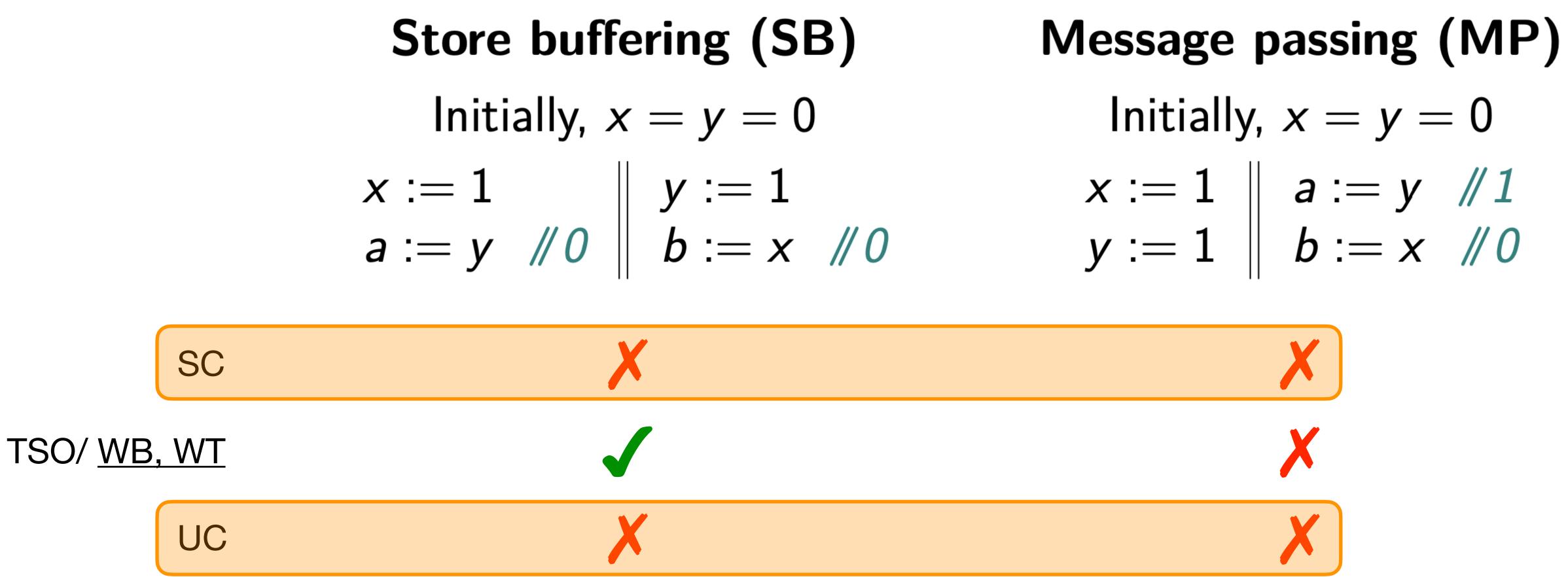

### Store buffering (SB) Initially, x = y = 0x := 1 $\| y := 1$ $a := y //0 \| b := x //0$

**B)**Message passing (MP)0Initially, x = y = 0x := 1a := yy := 1b := x

# Store buffering (SB) Initially, x = y = 0x := 1 || y := 1a := y //0 || b := x //0

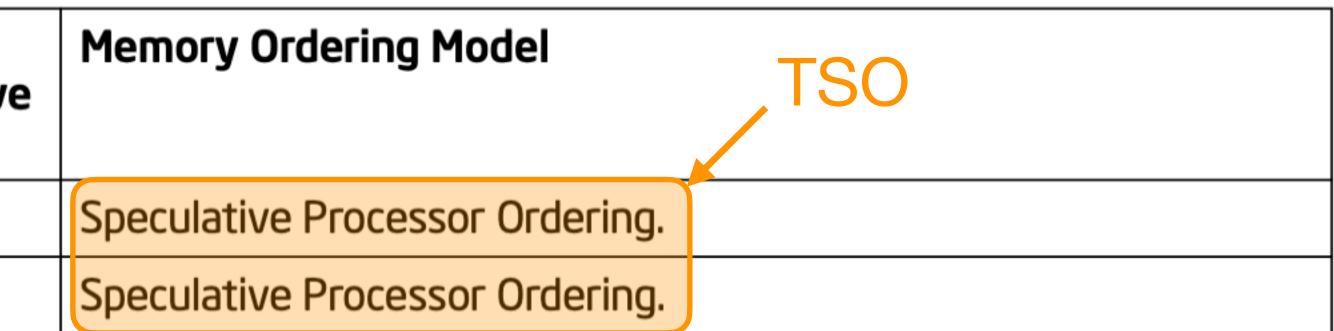

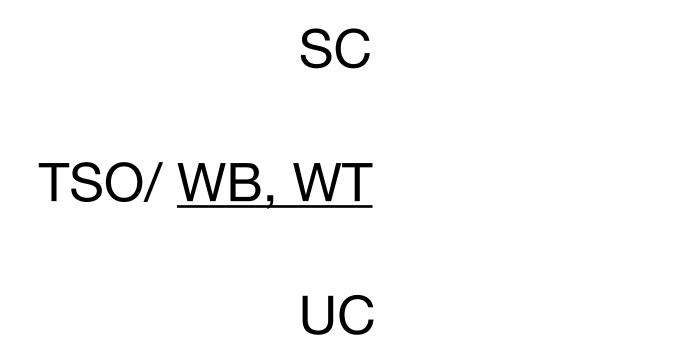

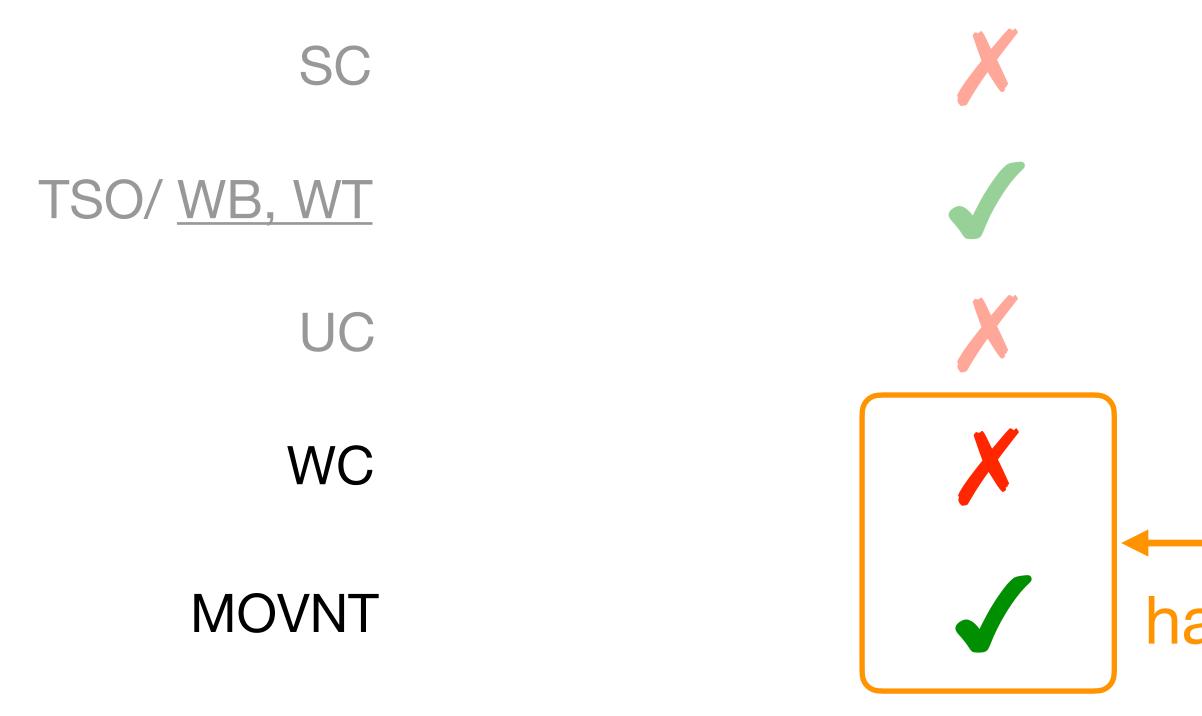

SC

- Message passing (MP) Initially, x = y = 0 $x := 1 \| a := y \|/1$  $y := 1 \| b := x \|/0$

# Store buffering (SB)

### Initially, x = y = 0 x := 1 || y := 1a := y //0 || b := x //0

- Message passing (MP)Initially, x = y = 0x := 1 || a := y //1y := 1 || b := x //0

- X

# Store buffering (SB) Initially, x = y = 0x := 1 || y := 1a := y //0 || b := x //0

SC

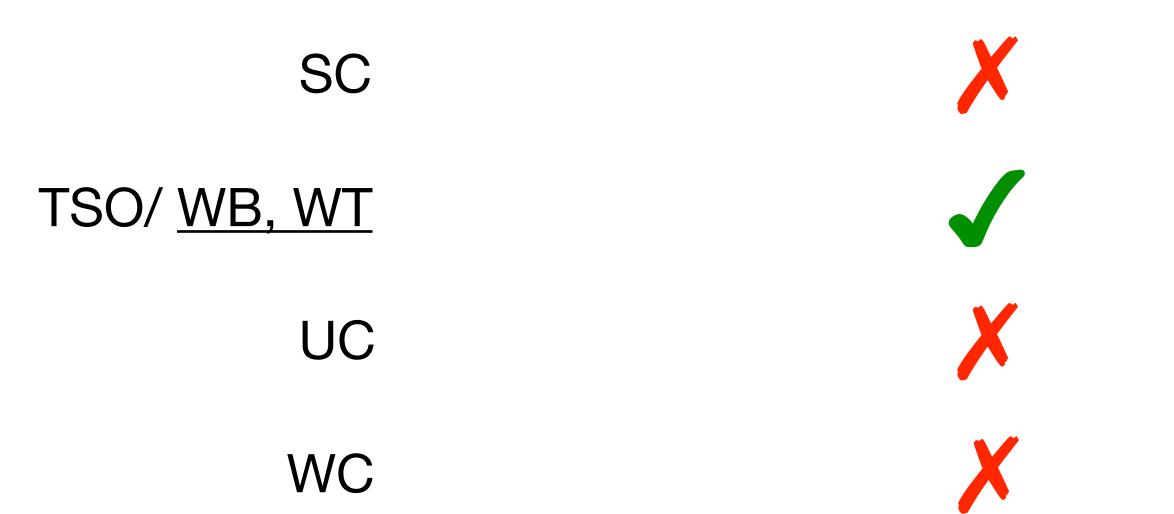

TSO/<u>WB, WT</u>

Message passing (MP) Initially, x = y = 0 $x := 1 \| a := y //1$  $y := 1 \| b := x //0$

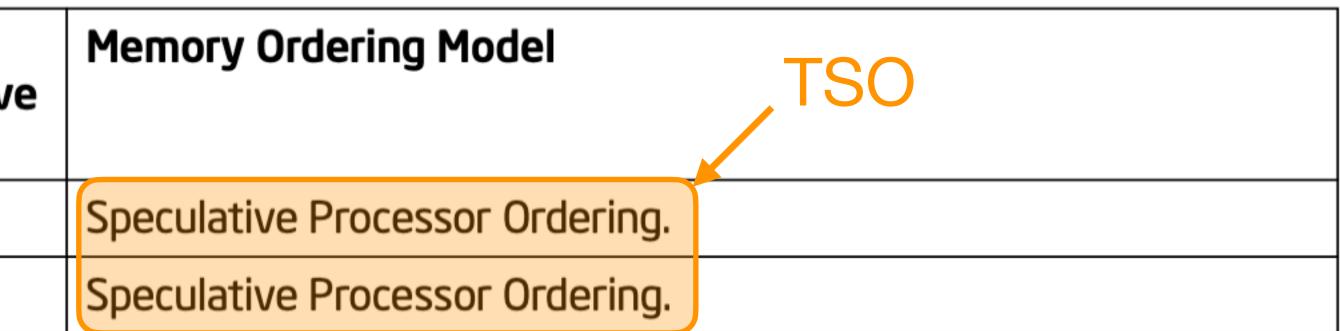

## **WB, WT** memory are subject to **TSO** consistency: write-read reordering

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads |

|-----------------------------|-----------|------------------------|--------------------------------|

| Write Through (WT)          | Yes       | No                     | Yes                            |

| Write Back (WB)             | Yes       | Yes                    | Yes                            |

### Memory Ordering Model

Speculative Processor Ordering.

Speculative Processor Ordering.

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads | Memory Ordering Model           | TSO |

|-----------------------------|-----------|------------------------|--------------------------------|---------------------------------|-----|

| Write Through (WT)          | Yes       | No                     | Yes                            | Speculative Processor Ordering. |     |

| Write Back (WB)             | Yes       | Yes                    | Yes                            | Speculative Processor Ordering. |     |

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculativ<br>Reads |

|-----------------------------|-----------|------------------------|-------------------------------|

| Write Through (WT)          | Yes       | No                     | Yes                           |

| Write Back (WB)             | Yes       | Yes                    | Yes                           |

### applies only to all-WB/ all-WT accesses, not mixed accesses

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable |     | Allows<br>Speculativ<br>Reads |

|-----------------------------|-----------|-----|-------------------------------|

| Write Through (WT)          | Yes       | No  | Yes                           |

| Write Back (WB)             | Yes       | Yes | Yes                           |

### applies only to all-WB/ all-WT accesses, not mixed accesses

**Write-through (WT)** — Writes and reads to and from system memory are cached. Reads come from cache lines on cache hits; read misses cause cache fills. Speculative reads are allowed. All writes are written to a cache line (when possible) and through to system memory. When writing through to memory, invalid cache lines are never filled, and valid cache lines are either filled or invalidated. Write combining is allowed. This type of cache-control is appropriate for frame buffers or when there are devices on the system bus that access system memory, but do not perform snooping of memory accesses. It enforces coherency between caches in the processors and system memory.

**Write-back (WB)** — Writes and reads to and from system memory are cached. Reads come from cache lines on cache hits; read misses cause cache fills. Speculative reads are allowed. Write misses cause cache line fills (in processor families starting with the P6 family processors), and writes are performed entirely in the cache, when possible. Write combining is allowed. The write-back memory type reduces bus traffic by eliminating many unnecessary writes to system memory. Writes to a cache line are not immediately forwarded to system memory; instead, they are accumulated in the cache. The modified cache lines are written to system memory later, when a write-back operation is performed. Write-back operations are triggered when cache lines need to be deallocated, such as when new cache lines are being allocated in a cache that is already full. They also are triggered by the mechanisms used to maintain cache consistency. This type of cache-control provides the best performance, but it requires that all devices that access system memory on the system bus be able to snoop memory accesses to ensure system memory and cache coherency.

### The extent of — WB/WT Specification in the Intel manual

## Store buffering (SB)

# Initially, x = y = 0x := 1 || y := 1a := y //0 || b := x //0

SC

### TSO/WB,WT

- Message passing (MP) Initially, x = y = 0 $x := 1 \| a := y \|/1$  $y := 1 \| b := x \|/0$

# Store buffering (SB)

### Initially, x = y = 0 x := 1 || y := 1a := y //0 || b := x //0

Message passing (MP)Initially, x = y = 0x := 1y := 1b := x //0

<u>UC</u> memory is subject to <u>SC</u> consistency semantics: no reordering

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads | Memory Ordering Model |

|-----------------------------|-----------|------------------------|--------------------------------|-----------------------|

| Strong Uncacheable<br>(UC)  | No        | No                     | No                             | Strong Ordering       |

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads | Memory Orderin  | g Model |

|-----------------------------|-----------|------------------------|--------------------------------|-----------------|---------|

| Strong Uncacheable<br>(UC)  | No        | No                     | No                             | Strong Ordering | ► SC    |

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads |

|-----------------------------|-----------|------------------------|--------------------------------|

| Strong Uncacheable<br>(UC)  | No        | No                     | No                             |

### applies only to all-UC accesses, not mixed accesses

### Memory Ordering Model

Strong Ordering SC

### Table 11-2. Memory Types and Their Properties

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads |

|-----------------------------|-----------|------------------------|--------------------------------|

| Strong Uncacheable<br>(UC)  | No        | No                     | No                             |

### applies only to all-UC accesses, not mixed accesses

**Strong Uncacheable (UC)** —System memory locations are not cached. All reads and writes appear on the system bus and are executed in program order without reordering. No speculative memory accesses, pagetable walks, or prefetches of speculated branch targets are made. This type of cache-control is useful for memory-mapped I/O devices. When used with normal RAM, it greatly reduces processor performance.

### Memory Ordering Model

Strong Ordering SC

> The extent of **UC** Specification in the Intel manual

# Store buffering (SB)

### Initially, x = y = 0 x := 1 || y := 1a := y //0 || b := x //0

Message passing (MP)Initially, x = y = 0x := 1y := 1b := x //0

## Store buffering (SB)

### Initially, x = y = 0 x := 1 || y := 1a := y //0 || b := x //0

### **WC** memory: write-write reordering on different locations

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads |

|-----------------------------|-----------|------------------------|--------------------------------|

| Write Combining (WC)        | No        | No                     | Yes                            |

write-write reordering on different locations

Table 11-2. Memory Types and Their Properties

### Memory Ordering Model

Weak Ordering. Available by programming MTRRs or by selecting it through the PAT.

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable | Allows<br>Speculative<br>Reads |

|-----------------------------|-----------|------------------------|--------------------------------|

| Write Combining (WC)        | No        | No                     | Yes                            |

write-write reordering on different locations

### applies only to all-WC accesses, not mixed accesses

Table 11-2. Memory Types and Their Properties

### Memory Ordering Model

### Weak Ordering. Available by programming MTRRs or by selecting it through the PAT.

| Memory Type and<br>Mnemonic | Cacheable | Writeback<br>Cacheable |     |

|-----------------------------|-----------|------------------------|-----|

| Write Combining (WC)        | No        | No                     | Yes |

### write-write reordering on different locations

### applies only to all-WC accesses, not mixed accesses

Write Combining (WC) — System memory locations are not cached (as with uncacheable memory) and coherency is not enforced by the processor's bus coherency protocol. Speculative reads are allowed. Writes may be delayed and combined in the write combining buffer (WC buffer) to reduce memory accesses. If the WC buffer is partially filled, the writes may be delayed until the next occurrence of a serializing event; such as an SFENCE or MFENCE instruction, CPUID or other serializing instruction, a read or write to uncached memory, an interrupt occurrence, or an execution of a LOCK instruction (including one with an XACQUIRE or XRELEASE prefix). In addition, an execution of the XEND instruction (to end a transactional region) evicts any writes that were buffered before the corresponding execution of the XBEGIN instruction (to begin the transactional region) before evicting any writes that were performed inside the transactional region.

This type of cache-control is appropriate for video frame buffers, where the order of writes is unimportant as long as the writes update memory so they can be seen on the graphics display. See Section 11.3.1, "Buffering of Write Combining Memory Locations," for more information about caching the WC memory type. This memory type is available in the Pentium Pro and Pentium II processors by programming the MTRRs; or in processor families starting from the Pentium III processors by programming the MTRRs or by selecting it through the PAT.

Table 11-2. Memory Types and Their Properties

### Memory Ordering Model

*j*e

Weak Ordering. Available by programming MTRRs or by selecting it through the PAT.

> The extent of WC Specification in the Intel manual

### What about Non-temporal Stores?

## Intel Manual: Non-temporal Stores

These SSE and SSE2 non-temporal store instructions minimize cache pollutions by treating the memory being accessed as the write combining (WC) type.

Using the WC semantics, the store transaction will be weakly ordered, meaning that the data may not be written to memory in program order,

### Intel Manual: Non-temporal Stores

These SSE and SSE2 non-temporal store instructions minimize cache pollutions by treating the memory being accessed as the write combining (WC) type.

Using the WC semantics, the store transaction will be weakly ordered, meaning that the data may not be written to memory in program order,

According to the Intel manual: Non-temporal stores have the same semantics as WC memory

## Intel Manual: Non-temporal Stores

These SSE and SSE2 non-temporal store instructions minimize cache pollutions by treating the memory being accessed as the write combining (WC) type.

Using the WC semantics, the store transaction will be weakly ordered, meaning that the data may not be written to memory in program order,

According to the Intel manual: Non-temporal stores have the same semantics as WC memory

Rut\_\_\_

### Store buffering (SB) Initially, x = y = 0 $x := 1 \qquad \parallel y := 1$ $a := y \parallel 0 \parallel b := x \parallel 0$

- Message passing (MP)Initially, x = y = 0x := 1 || a := y //1y := 1 || b := x //0

### **Ex86**: Extended Intel-x86 **Consistency** Semantics

# Store buffering (SB) Initially, x = y = 0x := 1 $\| y := 1$ $a := y //0 \| b := x //0$

# ) Message passing (MP) Initially, x = y = 0x := 1 || a := y //1y := 1 || b := x //0

WC & NT stores

have <u>different</u> semantics

## **Ex86**: Extended Intel-x86 **Consistency** Semantics

# Solution

# Validate the Ex86 Consistency Semantics!

# **Ex86 Validation**

### \* Validated Ex86 using the diy tool suite

### Extended the klitmus tool to allow for specifying memory types

# **Ex86 Validation**

- \* Validated Ex86 using the diy tool suite

- Extended the klitmus tool to allow for specifying memory types

- \* Built a test base of **over 2200 tests**

- Ran tests on various Intel-x86 CPU implementations ➡ e.g. corel5, corel6 and Xeon

- \* Ran each test at least 6 x 10<sup>8</sup> times; ran critical tests up to a few billion times

# Ex86 Validation

- \* Validated Ex86 using the diy tool suite

- Extended the klitmus tool to allow for specifying memory types

- Built a test base of over 2200 tests

- Ran tests on various Intel-x86 CPU implementations ➡ e.g. corel5, corel6 and Xeon

- \* Ran each test at least 6 x 10<sup>8</sup> times; ran critical tests up to a few billion times

- \* For more details see: http://diy.inria.fr/x86-memtype

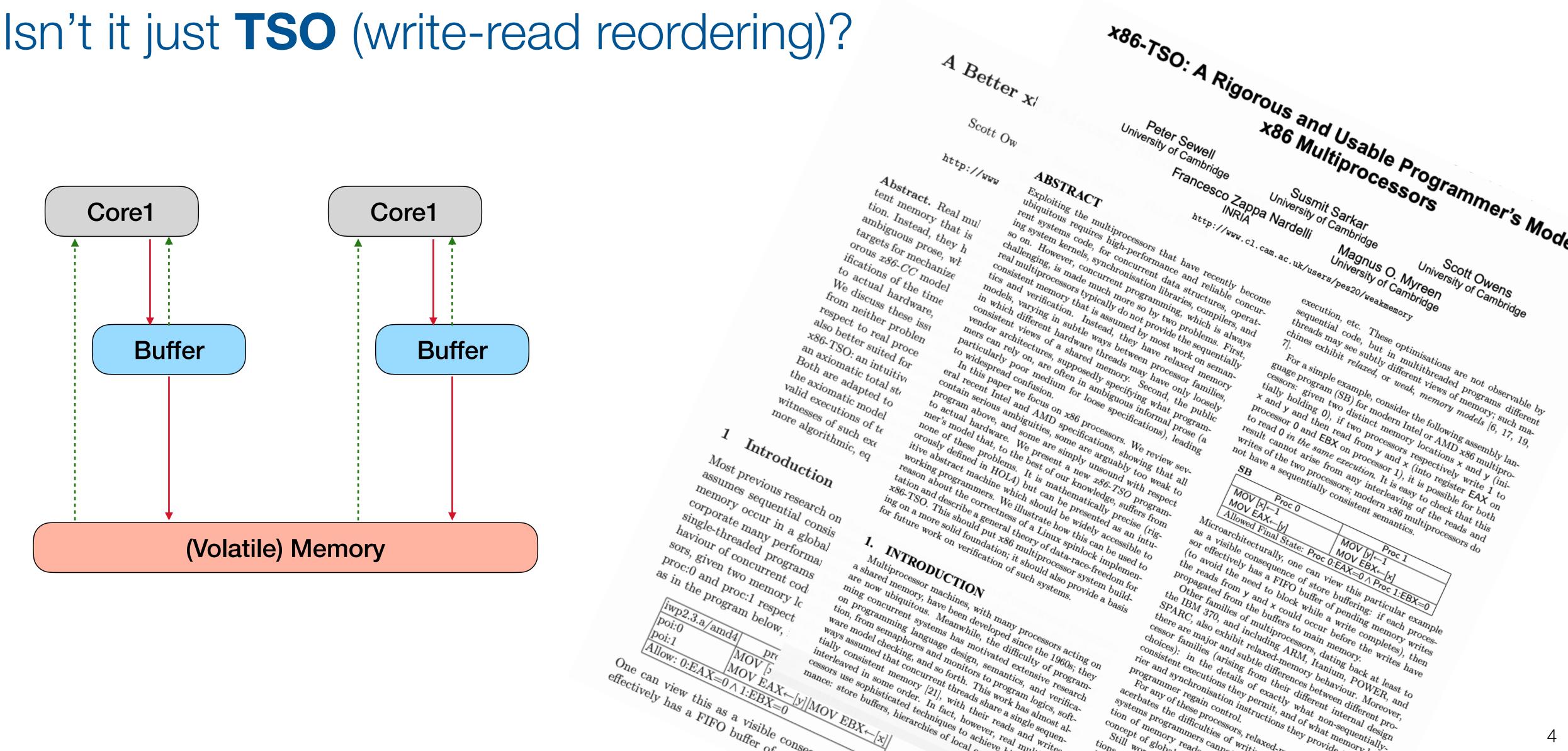

### Ex86 Semantics: Preserved Ordering

$W_{wb}$  $R_{wb,wt}|R_{uc,wc}|$ R Wwb Х X  $W_{wt,uc}$ sloc X  $W_{wc,nt}$ U,MF SF Х FL Х X X FO

Earlier in Program Order

sloc: Order preserved iffscl: Order preserved iffon the same locationon the same cache line

### Later in Program Order

| b | $W_{uc,wt}$ | $W_{wc,nt}$ | U,MF,SF | FL | FO  |

|---|-------------|-------------|---------|----|-----|

|   |             |             |         |    |     |

|   |             | sloc        |         |    | scl |

|   |             |             |         |    |     |

| С |             | sloc        |         |    | scl |

|   |             |             |         |    |     |

|   |             |             |         |    |     |

|   |             |             |         |    | X   |

|   |             | X           |         | X  | X   |

### Ex86 Semantics: Preserved Ordering

$W_{wb}$  $R_{wb,wt}|R_{uc,wc}|$ R  $W_{wb}$  $W_{wt,uc}$ Х  $W_{wc,nt}$ sloc X U,MF SF X FL Х X X FO

Earlier in Program Order

sloc: Order preserved iffscl: Order preserved iffon the same locationon the same cache line

### Later in Program Order

| b | $W_{uc,wt}$ | $W_{wc,nt}$ | U,MF,SF | FL | FO  |

|---|-------------|-------------|---------|----|-----|

|   |             |             |         |    |     |

|   |             | sloc        |         |    | scl |

|   |             |             |         |    |     |

| С |             | sloc        |         |    | scl |

|   |             |             |         |    |     |

|   |             |             |         |    |     |

|   |             |             |         |    | X   |

|   |             | X           |         | X  | X   |

### Ex86 Semantics: Preserved Ordering

$W_{wb}$  $R_{wb,wt}|R_{uc,wc}|$ R Wwb Х  $W_{wt,uc}$ X X  $W_{wc,nt}$ sloc U,MF SF Х FL Х X X FO

Earlier in Program Order

sloc: Order preserved iffscl: Order preserved iffon the same locationon the same cache line

### Later in Program Order

| b | $W_{uc,wt}$ | $W_{wc,nt}$ | U,MF,SF | FL | FO  |

|---|-------------|-------------|---------|----|-----|

|   |             |             |         |    |     |

|   |             | sloc        |         |    | scl |

|   |             |             |         |    |     |

| С |             | sloc        |         |    | scl |

|   |             |             |         |    |     |

|   |             |             |         |    |     |

|   |             |             |         |    | X   |

|   |             | X           |         | X  | X   |

### What about Intel-x86 *Persistency* Semantics?

# Computer Storage

# Computer Storage

# Computer Storage

### X slow √ persistent

# What is Non-Volatile Memory (NVM)?

# What is Non-Volatile Memory (NVM)?

### NVM: Hybrid Storage + Memory

Best of both worlds:

✓ persistent (like HDD)

✓ fast, random access (like RAM)

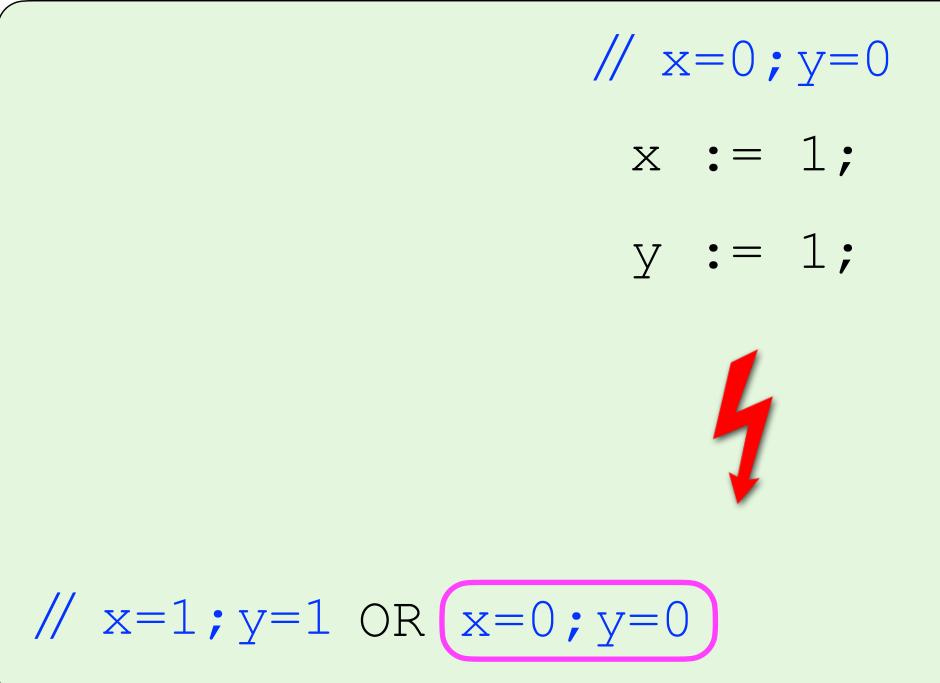

### // x=0;y=0

- x := 1;

- y := 1;

### // x=0;y=0

- x := 1;

- y := 1;

**!!** Execution continues *ahead of persistence* - asynchronous persists

**!!** Execution continues *ahead of persistence* - asynchronous persists

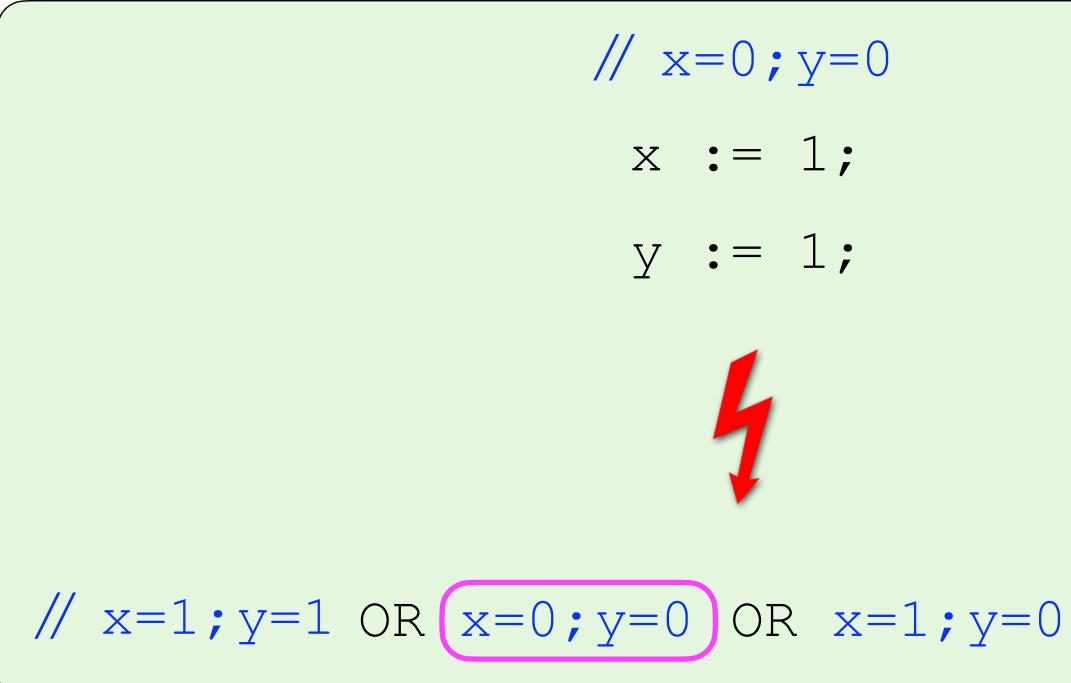

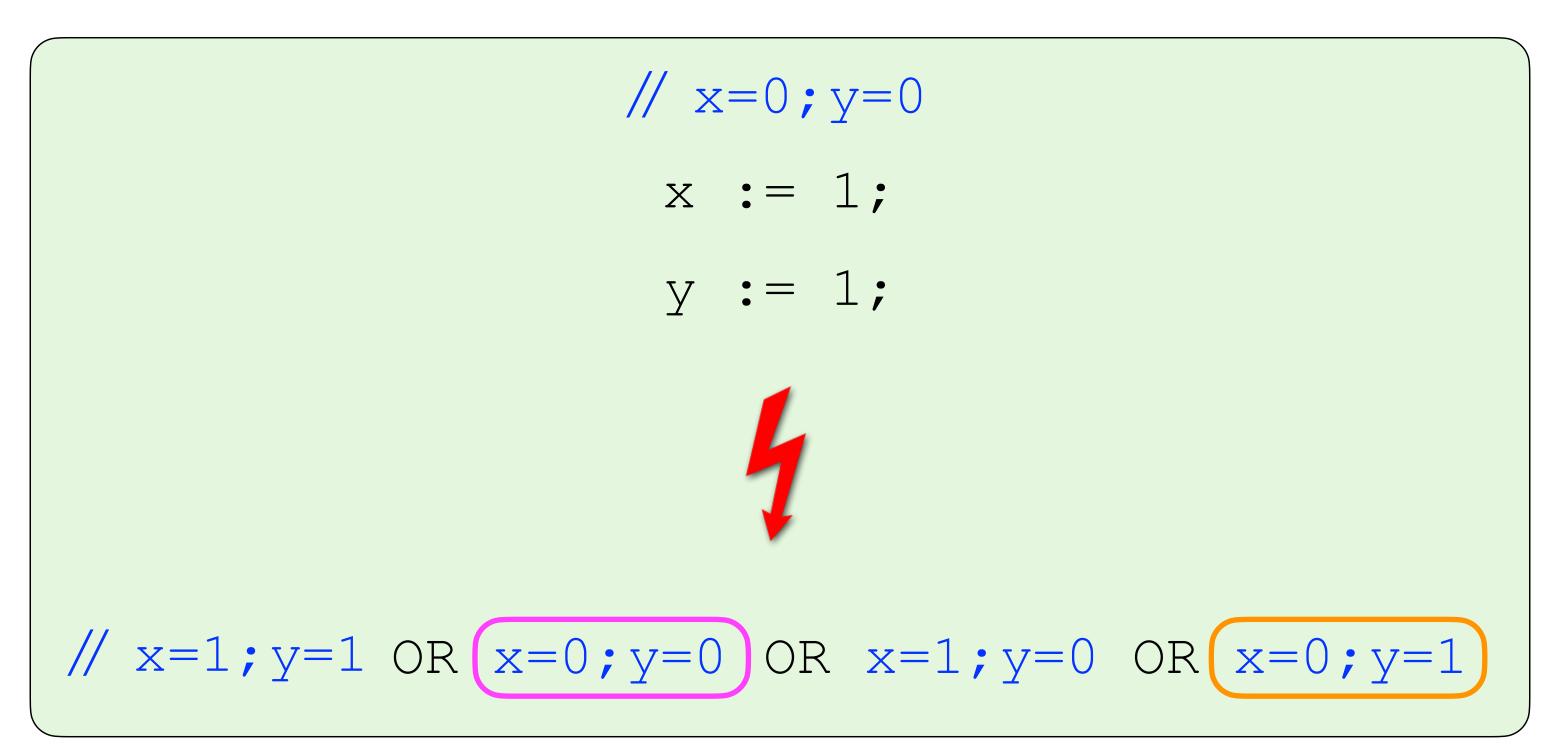

### // x=0;y=0

- x := 1;

- y := 1;

**!!** Execution continues *ahead of persistence* - asynchronous persists

!! Writes may persist out of order

### **Consistency Model**

the order in which writes are *made visible* to other threads

the order in which writes are *made visible* to other threads

the order in which writes are *persisted* to NVM

### **Consistency Model**

### **Persistency Model**

the order in which writes are *made visible* to other threads

the order in which writes are *persisted* to NVM

**Full Semantics** Consistency + Persistency Model

### **Consistency Model**

### **Persistency Model**

# PEx86 (Persistent Extended x86):

- Formal consistency + Persistency semantics of

- Intel-x86 architectures

- including

- non-temporal stores & memory types

### **PEx86**: Persistent Extended Intel-x86 Semantics

| $x, y \in Loc_{wb}$      | $x, y \in Loc_{wb}$        | $x, x', y \in Loc_{wb}$ | $x, x', y \in Loc_{wb}$    | $x, x', y \in Loc_{wb}$       |

|--------------------------|----------------------------|-------------------------|----------------------------|-------------------------------|

| x := 1                   | x := 1                     | x := 1                  | x := 1                     | x := 1                        |

| y := 1                   | clflush x                  | clflushopt x'           | -                          | <b>clflushopt</b> <i>x'</i> ; |

|                          | y := 1                     | y := 1                  | xchg(y,1)                  | sfence                        |

|                          |                            |                         |                            | y := 1                        |

| rec: $x, v \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $x.v \in \{0.1\}$  | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=1$    |

| x∈Loc <sub>uc∪wt</sub>     | $x \in Loc_{wc},$        | $x \in Loc_{wc},$          | $x \in \operatorname{Loc}_{wb \cup wt \cup wc}$ | x∈Loc <sub>wb∪wt∪wc</sub>   |

|----------------------------|--------------------------|----------------------------|-------------------------------------------------|-----------------------------|

| y∈Loc                      | y∈Loc <sub>wc∪wb</sub>   | y∈Loc <sub>uc∪wt</sub>     | y∈Loc <sub>uc∪wt</sub>                          | y∈Loc <sub>wc∪wb</sub>      |

| x := 1                     | x := 1                   | x := 1                     | x := 1                                          | x := 1                      |

| y := 1                     | y := 1                   | y := 1                     | <i>х</i> := <sub>NT</sub> 2                     | <i>x</i> := <sub>NT</sub> 2 |

|                            |                          |                            | y := 1                                          | sfence                      |

|                            |                          |                            |                                                 | y := 1                      |

| rec: $y=1 \Rightarrow x=1$ | rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=2$                      | rec: $y=1 \Rightarrow x=2$  |

### **PEx86**: Persistent Extended Intel-x86 Semantics

| $x, y \in Loc_{wb}$      | $x, y \in Loc_{wb}$        | $x, x', y \in Loc_{wb}$  | $x, x', y \in Loc_{wb}$    | $x, x', y \in Loc_{wb}$    |

|--------------------------|----------------------------|--------------------------|----------------------------|----------------------------|

| x := 1                   | x := 1                     | x := 1                   | x := 1                     | x := 1                     |

| y := 1                   | clflush x                  | clflushopt x'            | clflushopt x'              | clflushopt x';             |

|                          | y := 1                     | y := 1                   | xchg(y,1)                  | sfence                     |

|                          |                            |                          |                            | y := 1                     |

| rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=1$ |

| x∈Loc <sub>uc∪wt</sub>     | $x \in Loc_{wc},$        | $x \in Loc_{wc},$          | $x \in \operatorname{Loc}_{wb \cup wt \cup wc}$ | x∈Loc <sub>wb∪wt∪wc</sub>  |

|----------------------------|--------------------------|----------------------------|-------------------------------------------------|----------------------------|

| y∈Loc                      | y∈Loc <sub>wc∪wb</sub>   | y∈Loc <sub>uc∪wt</sub>     | y∈Loc <sub>uc∪wt</sub>                          | y∈Loc <sub>wc∪wb</sub>     |

| x := 1                     | x := 1                   | x := 1                     | x := 1                                          | x := 1                     |

| y := 1                     | y := 1                   | y := 1                     | $x :=_{NT} 2$                                   | $x :=_{NT} 2$              |

|                            |                          |                            | y := 1                                          | sfence                     |

|                            |                          |                            |                                                 | y := 1                     |

| rec: $y=1 \Rightarrow x=1$ | rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=2$                      | rec: $y=1 \Rightarrow x=2$ |

### **PEx86**: Persistent Extended Intel-x86 Semantics

| $x, y \in Loc_{wb}$      | $x, y \in Loc_{wb}$        | $x, x', y \in Loc_{wb}$          | $x, x', y \in Loc_{wb}$    | $x, x', y \in Loc_{wb}$    |

|--------------------------|----------------------------|----------------------------------|----------------------------|----------------------------|

| x := 1                   | x := 1                     | x := 1                           | x := 1                     | x := 1                     |

| y := 1                   |                            |                                  |                            | clflushopt x';             |

|                          | y := 1                     | y := 1                           | xchg(y, 1)                 | sfence                     |

|                          |                            |                                  |                            | y := 1                     |

| rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: <i>x</i> , <i>y</i> ∈ {0,1} | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=1$ |

| x∈Loc <sub>uc∪wt</sub>     | $x \in Loc_{wc},$        | $x \in Loc_{wc},$          | $x \in \operatorname{Loc}_{wb \cup wt \cup wc}$ | x ∈ Loc <sub>wbUwtUwc</sub> |

|----------------------------|--------------------------|----------------------------|-------------------------------------------------|-----------------------------|

| y∈Loc                      | y∈Loc <sub>wc∪wb</sub>   | y∈Loc <sub>uc∪wt</sub>     | y∈Loc <sub>uc∪wt</sub>                          | y∈Loc <sub>wc∪wb</sub>      |

| x := 1                     | x := 1                   | x := 1                     | x := 1                                          | x := 1                      |

| y := 1                     | y := 1                   | y := 1                     | $x :=_{NT} 2$                                   | $x :=_{NT} 2$               |

|                            |                          |                            | y := 1                                          | sfence                      |

|                            |                          |                            |                                                 | y := 1                      |

| rec: $y=1 \Rightarrow x=1$ | rec: $x, y \in \{0, 1\}$ | rec: $y=1 \Rightarrow x=1$ | rec: $y=1 \Rightarrow x=2$                      | rec: $y=1 \Rightarrow x=2$  |

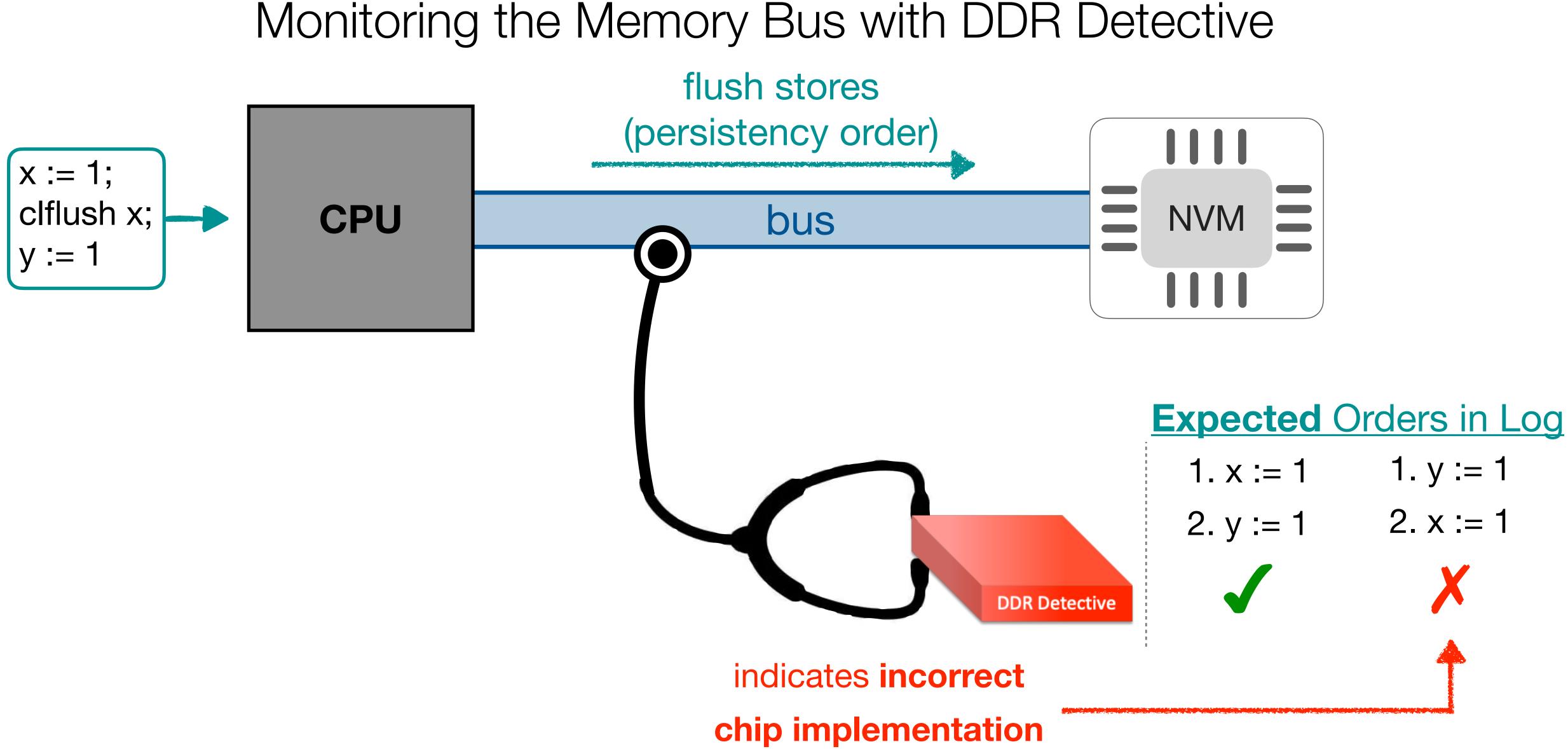

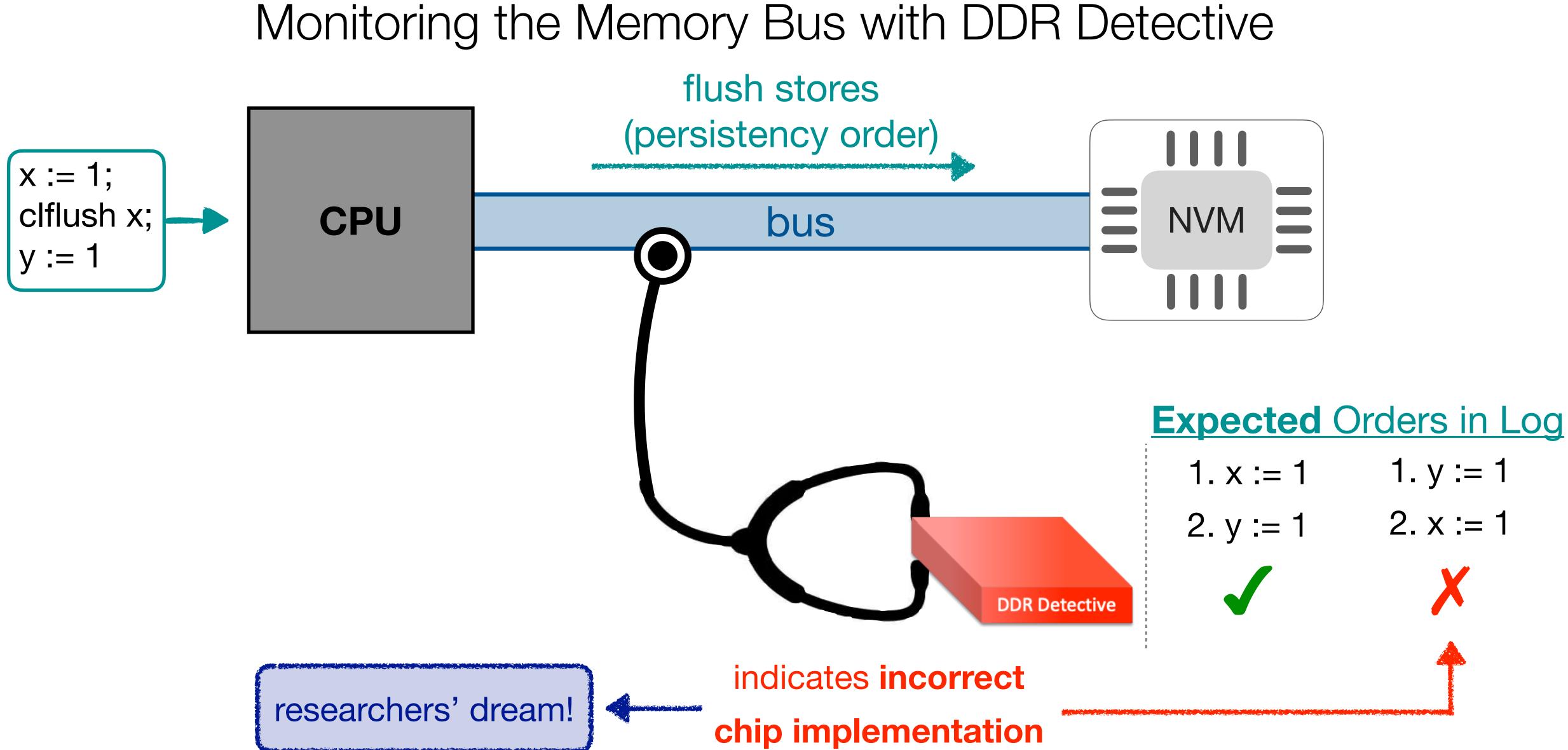

### How to test for post-crash behaviours?

Persistency Validation?

How to test for post-crash behaviours?

1. Contrive crashes (e.g. pull the plug) at crucial times

Persistency Validation?

- How to test for post-crash behaviours?

- 1. Contrive crashes (e.g. pull the plug) at crucial times

Persistency Validation?

Do this for *thousands* of tests, each for *hundreds of millions* of times  $\ge 10^{11}$  crashes

Infeasible !

- How to test for post-crash behaviours?

- 1. Contrive crashes (e.g. pull the plug) at crucial times

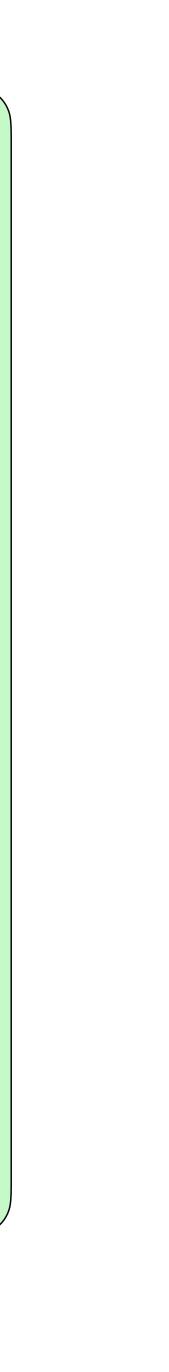

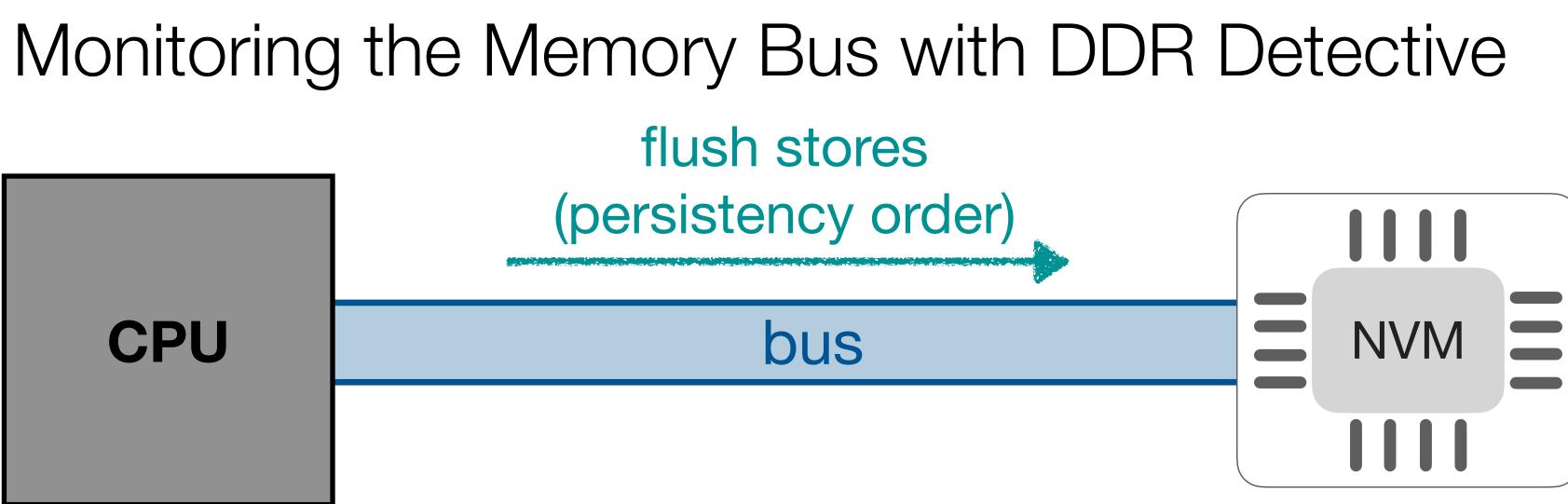

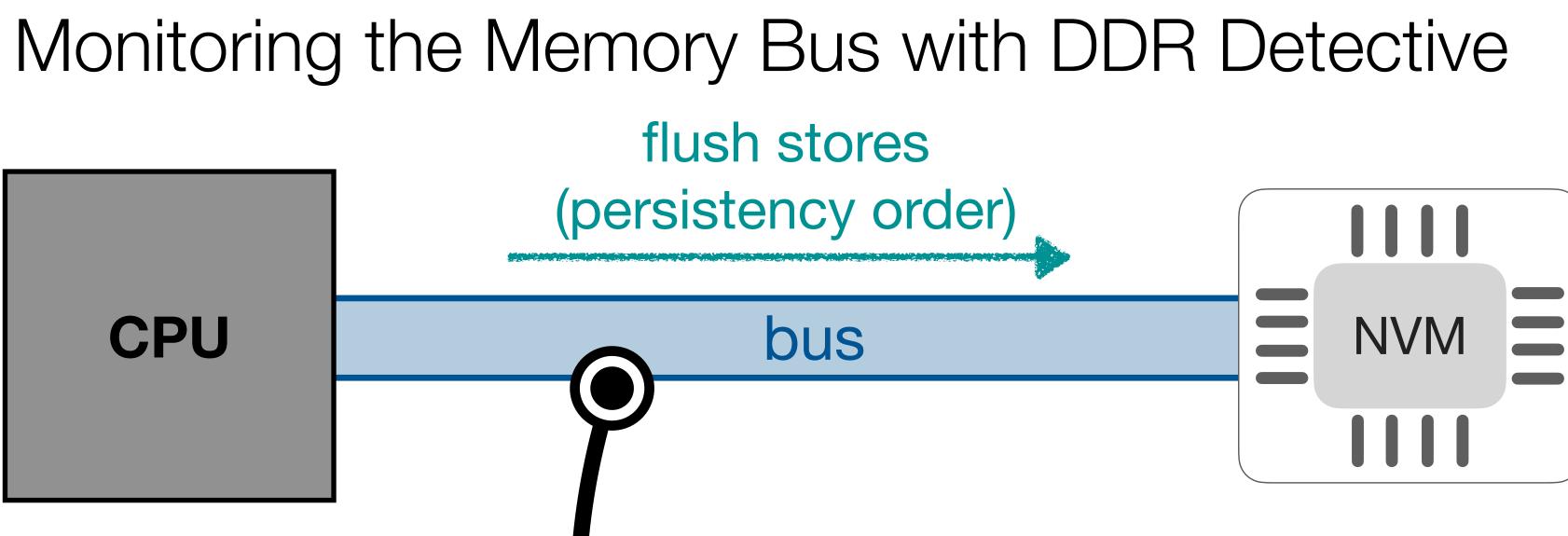

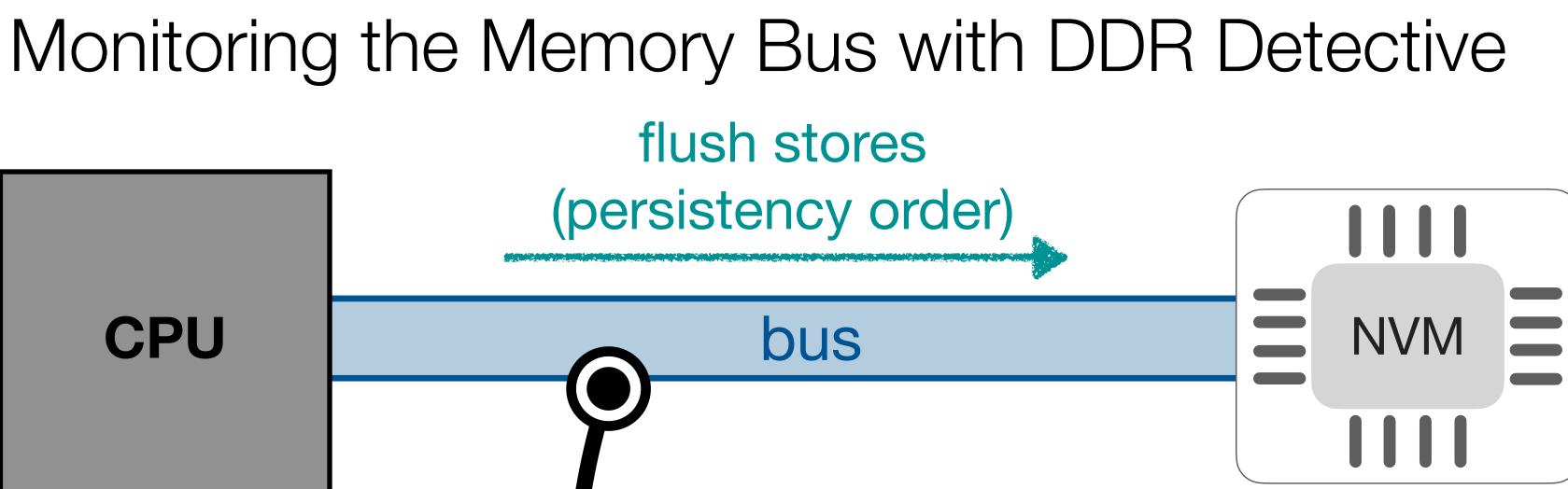

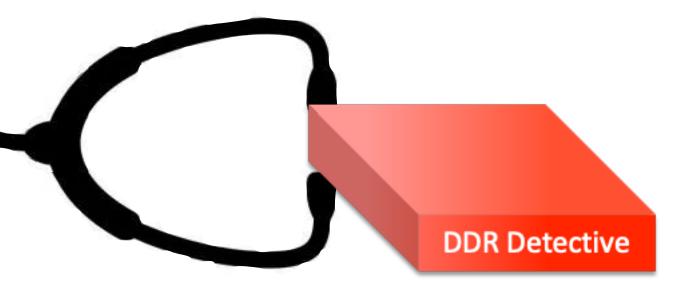

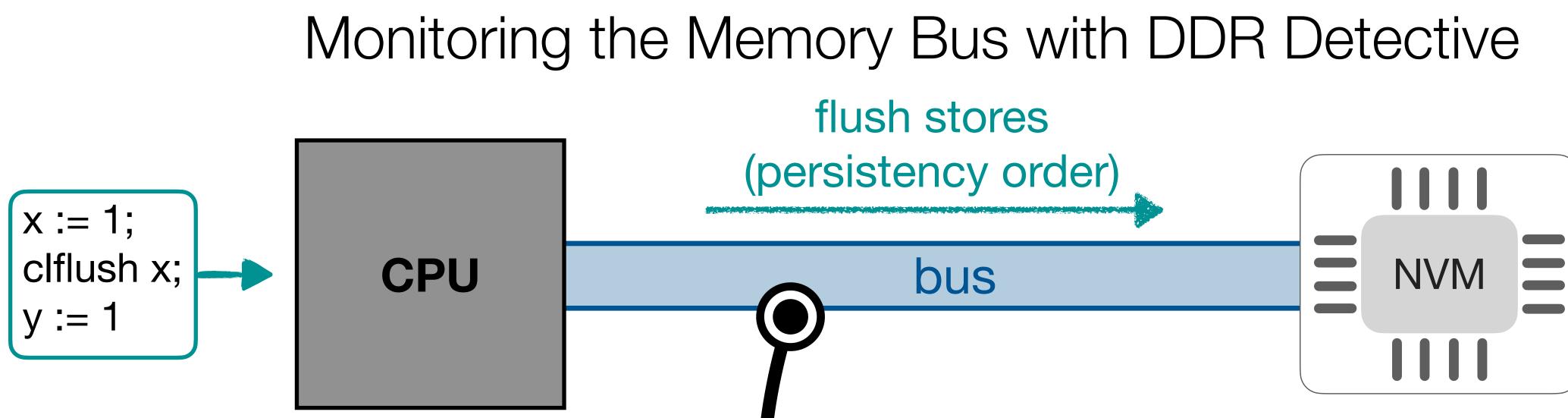

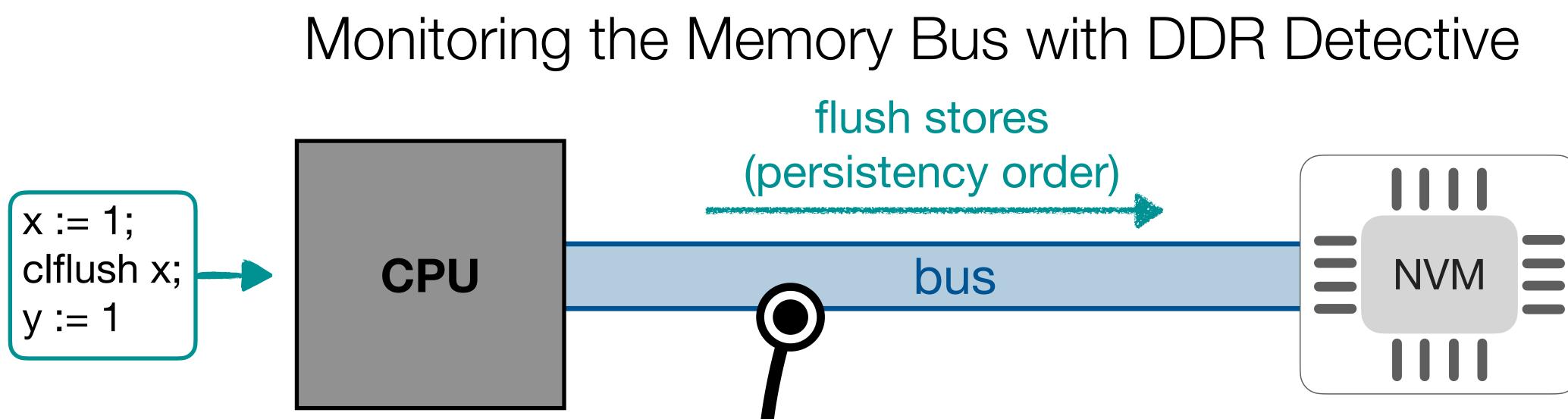

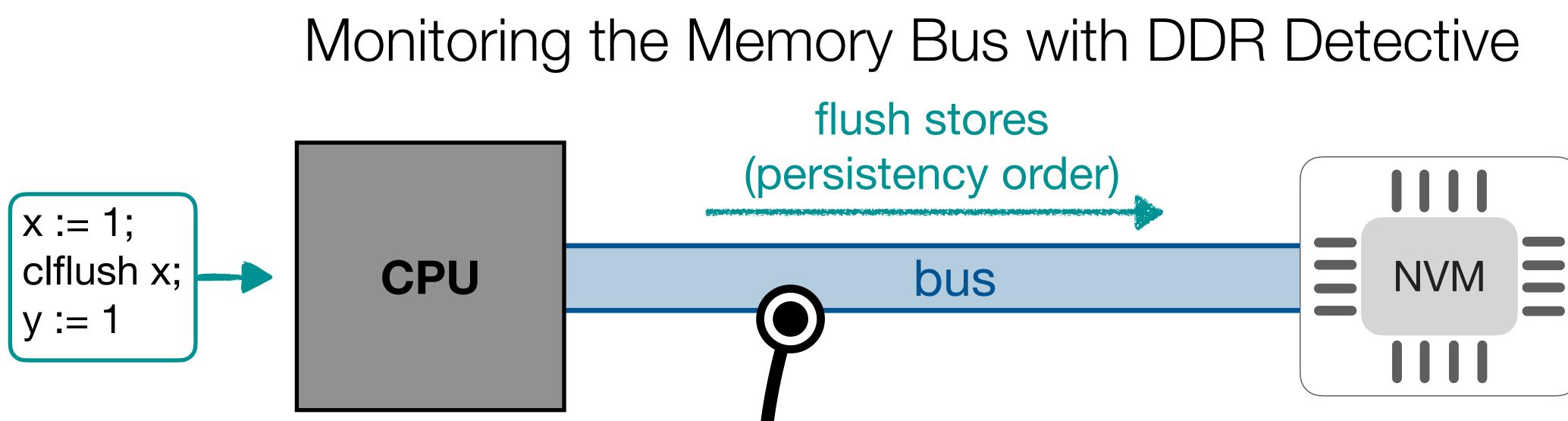

2. Directly monitor the memory bus for the order of stores

Persistency Validation?

- Do this for *thousands* of tests, each for *hundreds of millions* of times  $\ge 10^{11}$  crashes

- Infeasible !

**Promising** !

- How to test for post-crash behaviours?

- 1. Contrive crashes (e.g. pull the plug) at crucial times

Do this for *thousands* of tests, each for *hundreds of millions* of times  $\ge 10^{11}$  crashes

2. Directly monitor the memory bus for the order of stores

Persistency Validation?

### Infeasible !

**Promising** !

- Listen

- Log stores

- Observe order

- Listen

- Log stores

- Observe order

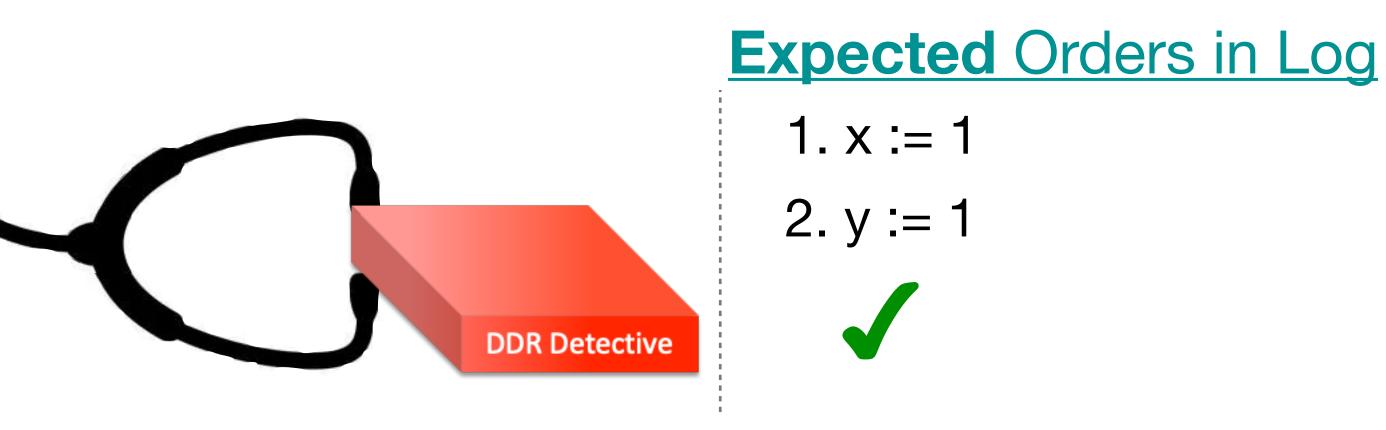

### **Expected** Orders in Log 1. x := 1 1. y := 1 2. x := 1 2. y := 1

### **Observed** Orders in Log

### **Observed** Orders in Log 1. x := 1 2. y := 1

**Observed** Orders in Log 1. x := 1 1. y := 1 2. x := 1 2. y := 1

### **Observed** Orders in Log 1. y := 1 2. x := 1

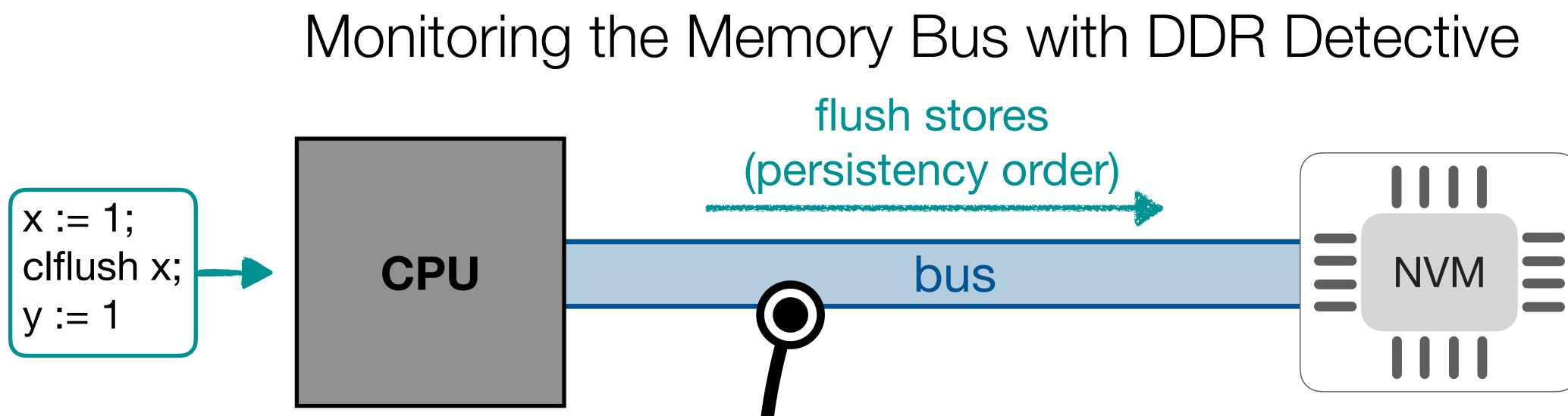

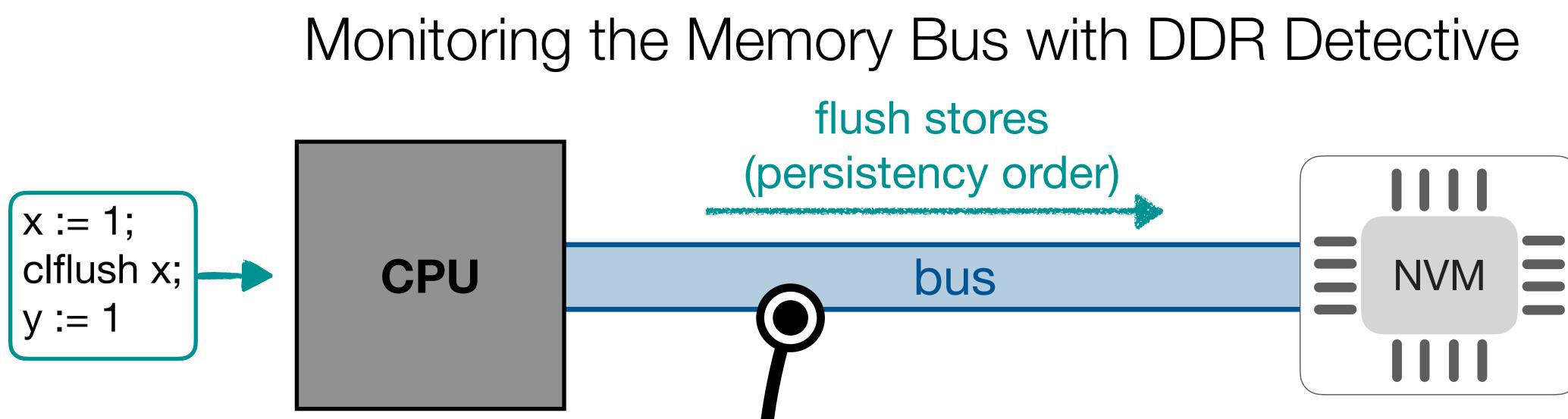

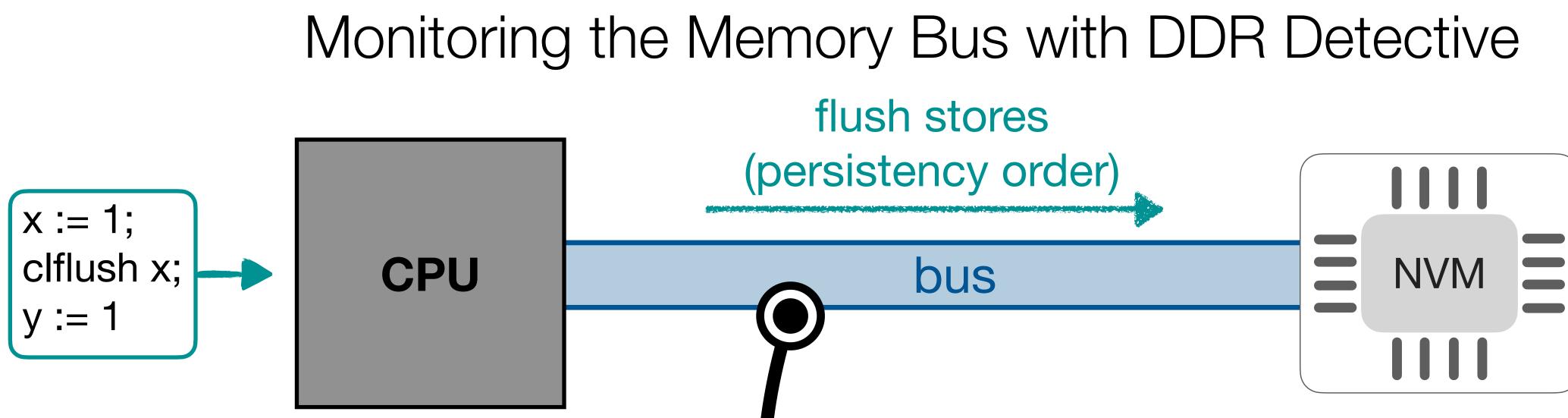

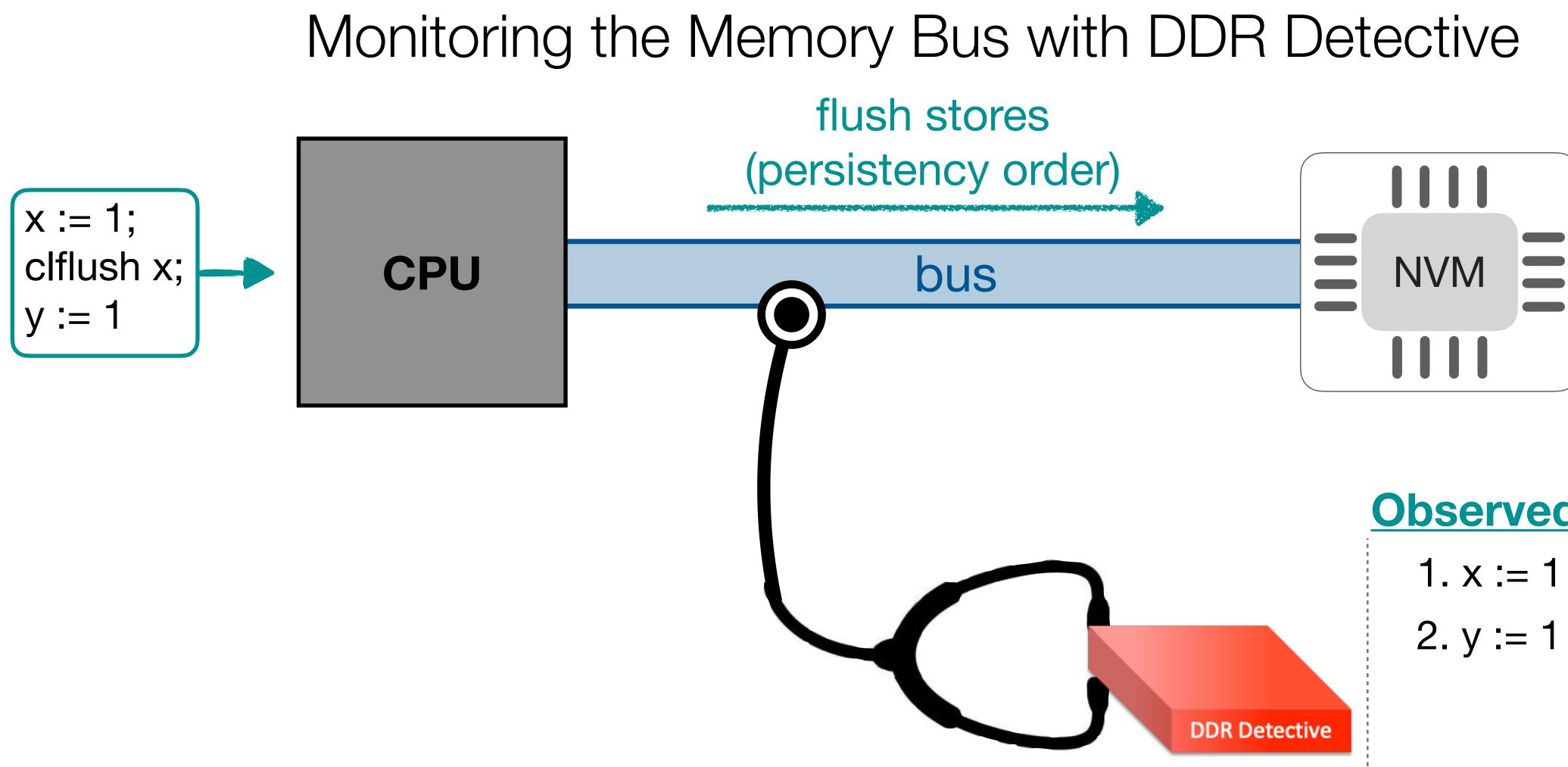

## Not so fast...

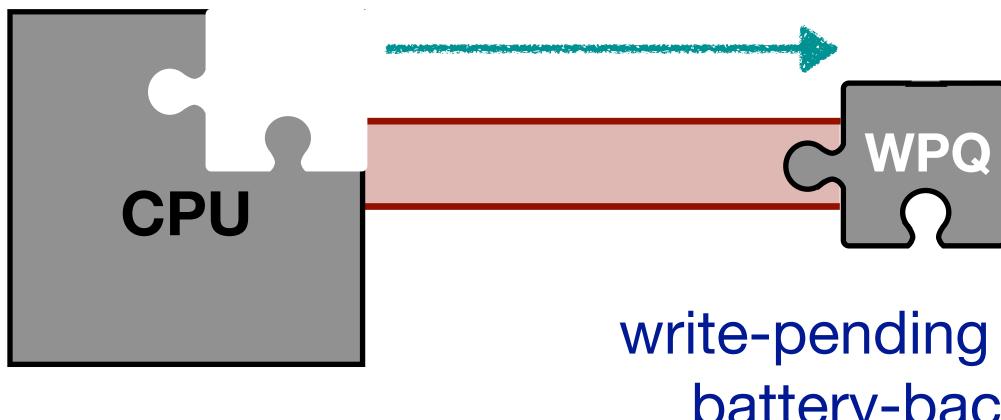

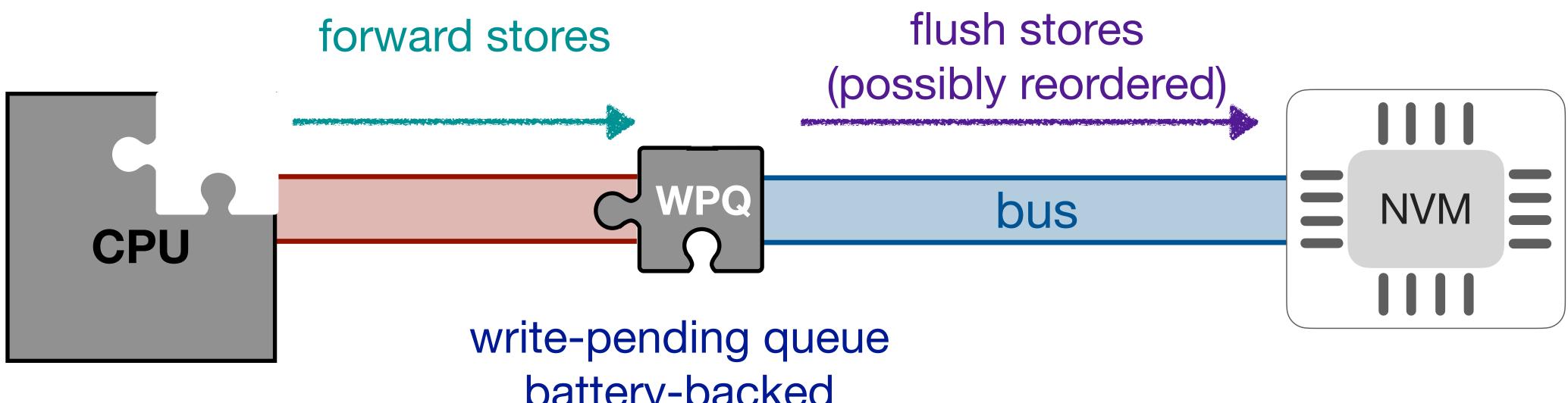

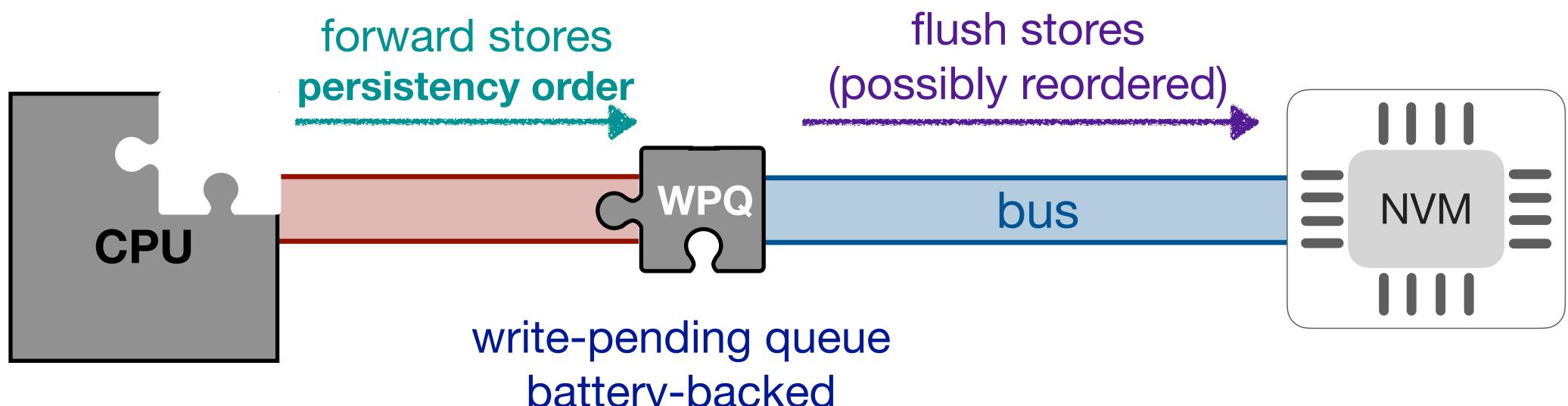

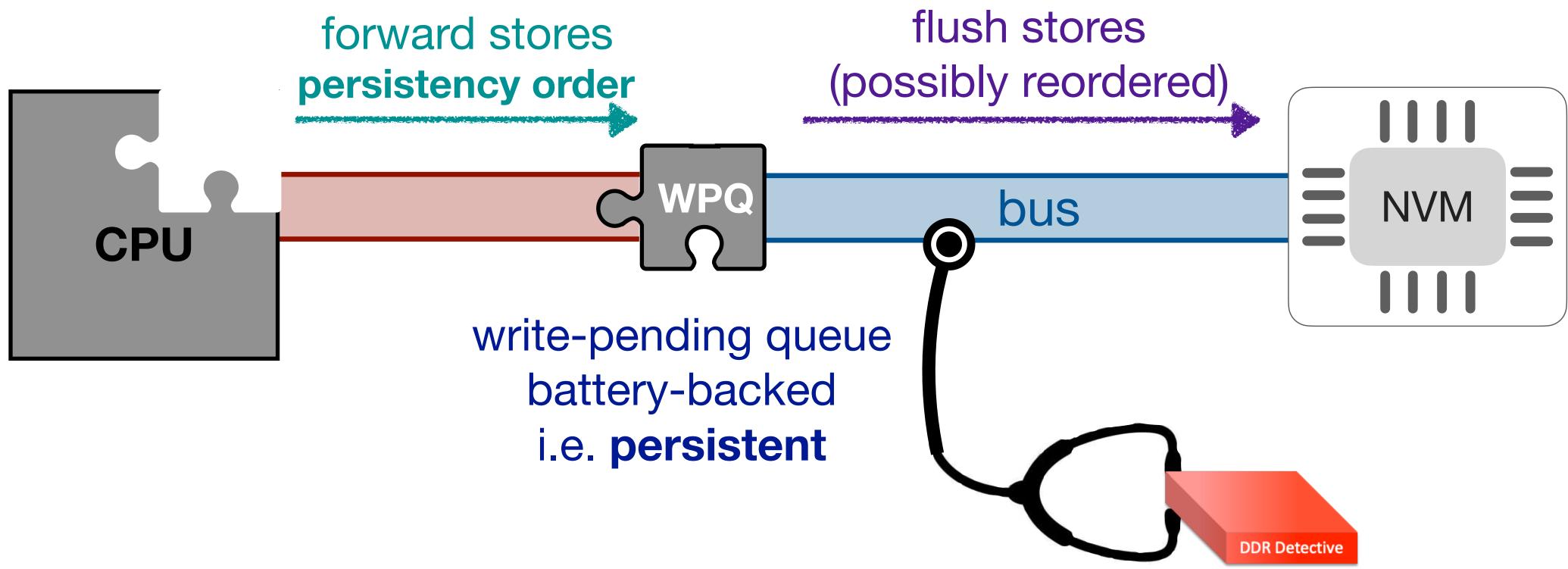

### forward stores

write-pending queue battery-backed i.e. persistent

battery-backed i.e. persistent

battery-backed i.e. persistent

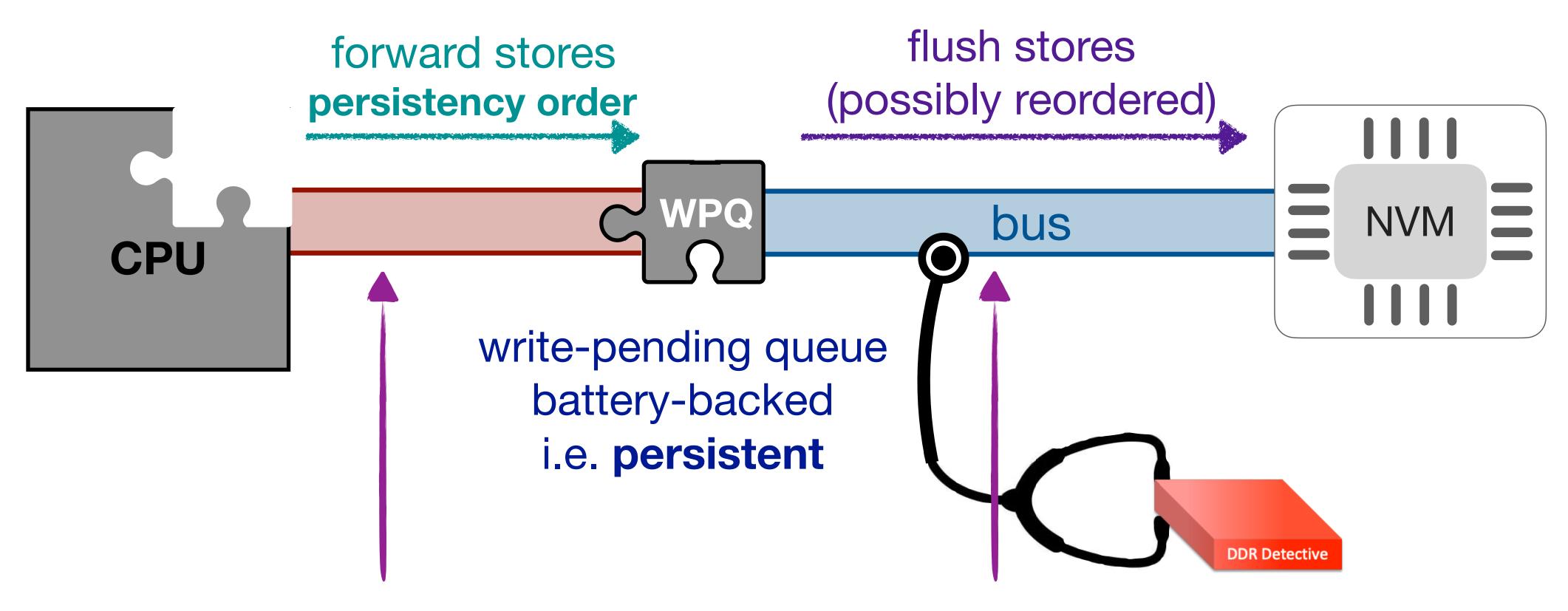

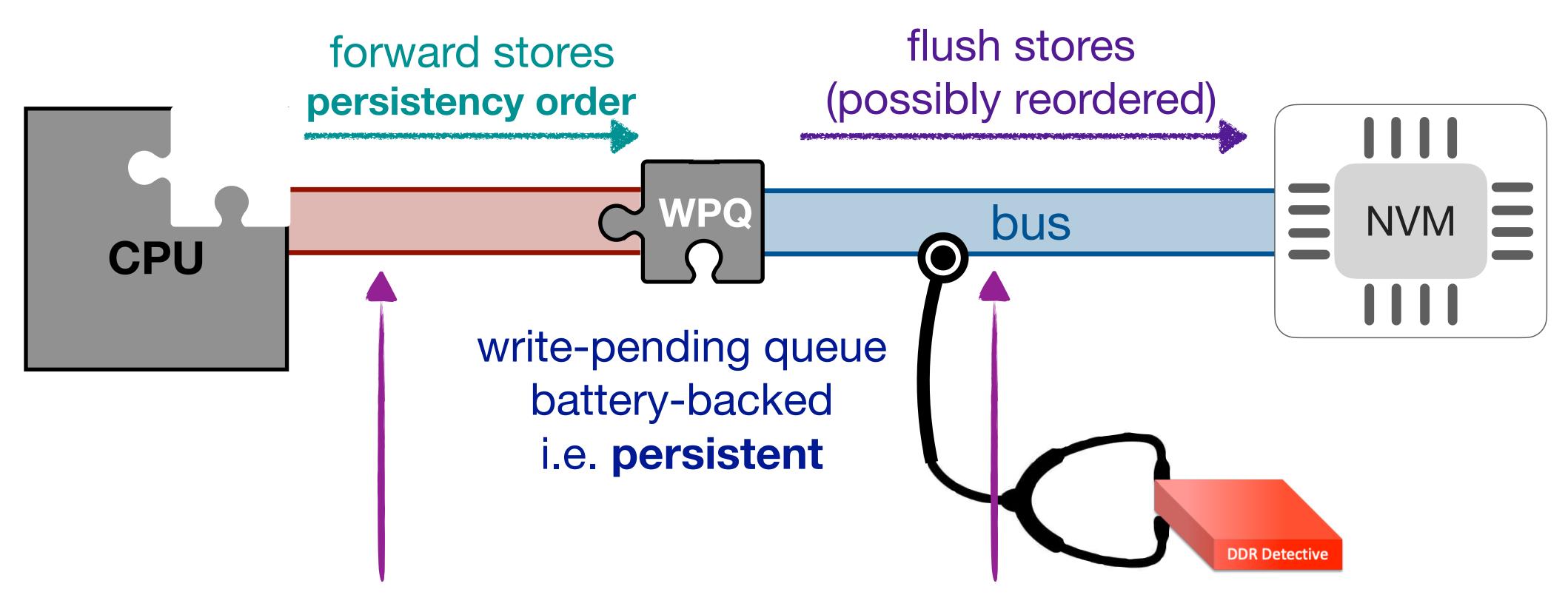

must monitor here (unclear how to do)

## Not so fast...

too late to monitor

must monitor here (unclear how to do)

Inconclusive validation

## Not so fast...

too late to monitor

# Conclusions

- Memory types (WB, WT, WC, UC)

- Non-temporal stores

- \* Formalised Ex86 both operationally & declaratively, and proved them equivalent \* Formalised <u>PEx86</u> both *operationally* & *declaratively*, and proved them *equivalent* \* Empirically validated Ex86 through extensive testing

Attempted to validate PEx86; inconclusive results

Developed Ex86 and PEx86: extensive Intel-x86 consistency and persistency models

# Conclusions

- Memory types (WB, WT, WC, UC)

- Non-temporal stores

- \* Formalised Ex86 both operationally & declaratively, and proved them equivalent

### \* Empirically validated Ex86 through extensive testing

Attempted to validate PEx86; inconclusive results

Developed Ex86 and PEx86: extensive Intel-x86 consistency and persistency models

\* Formalised <u>PEx86</u> both *operationally* & *declaratively*, and proved them *equivalent*

### Thank You for Listening!

SoundAndComplete.org