### **Clio: A Hardware-Software Co-Designed Disaggregated Memory System**

Zhiyuan Guo\*, Yizhou Shan\* (\* equal contribution) Xuhao Luo, Yutong Huang, Yiying Zhang

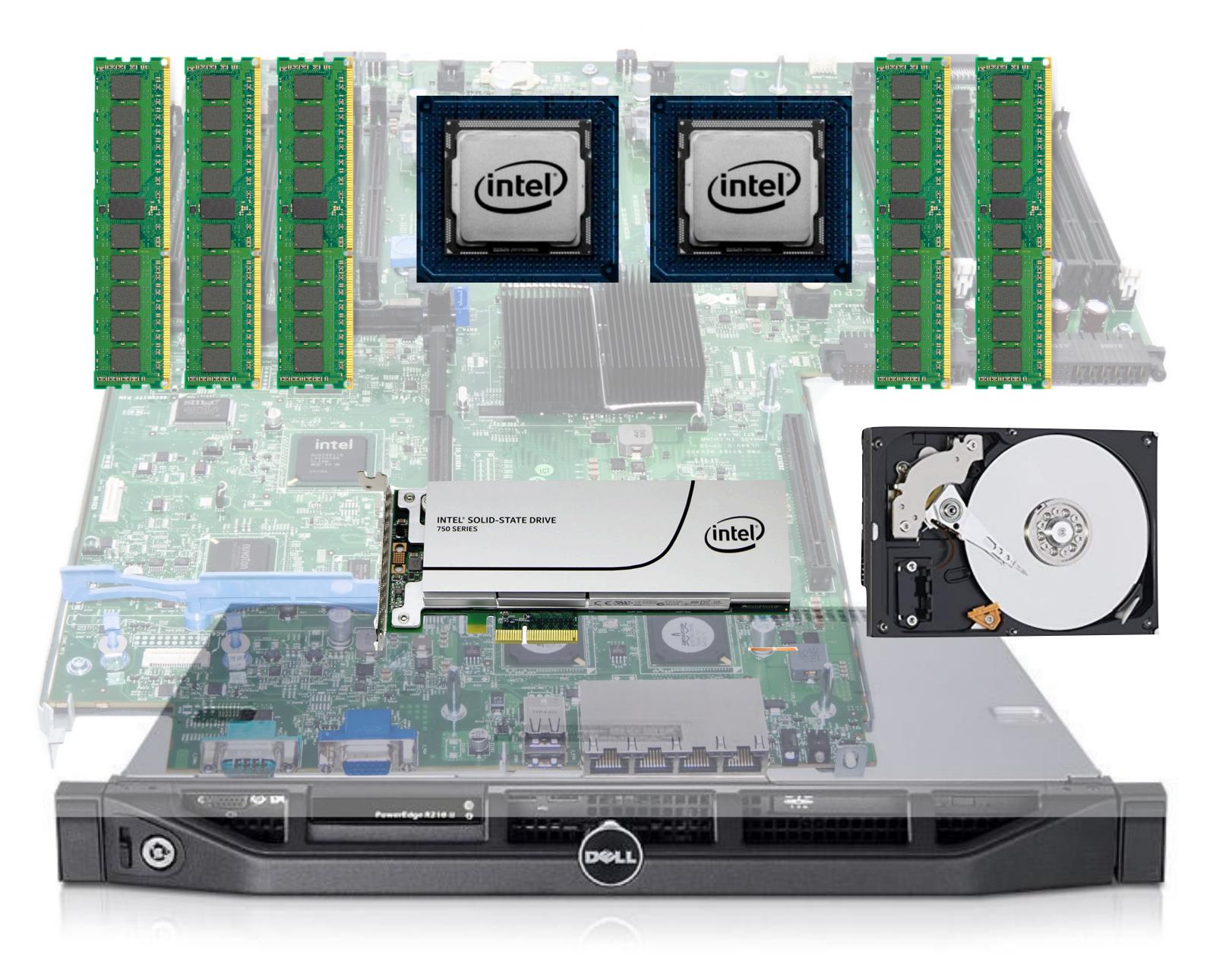

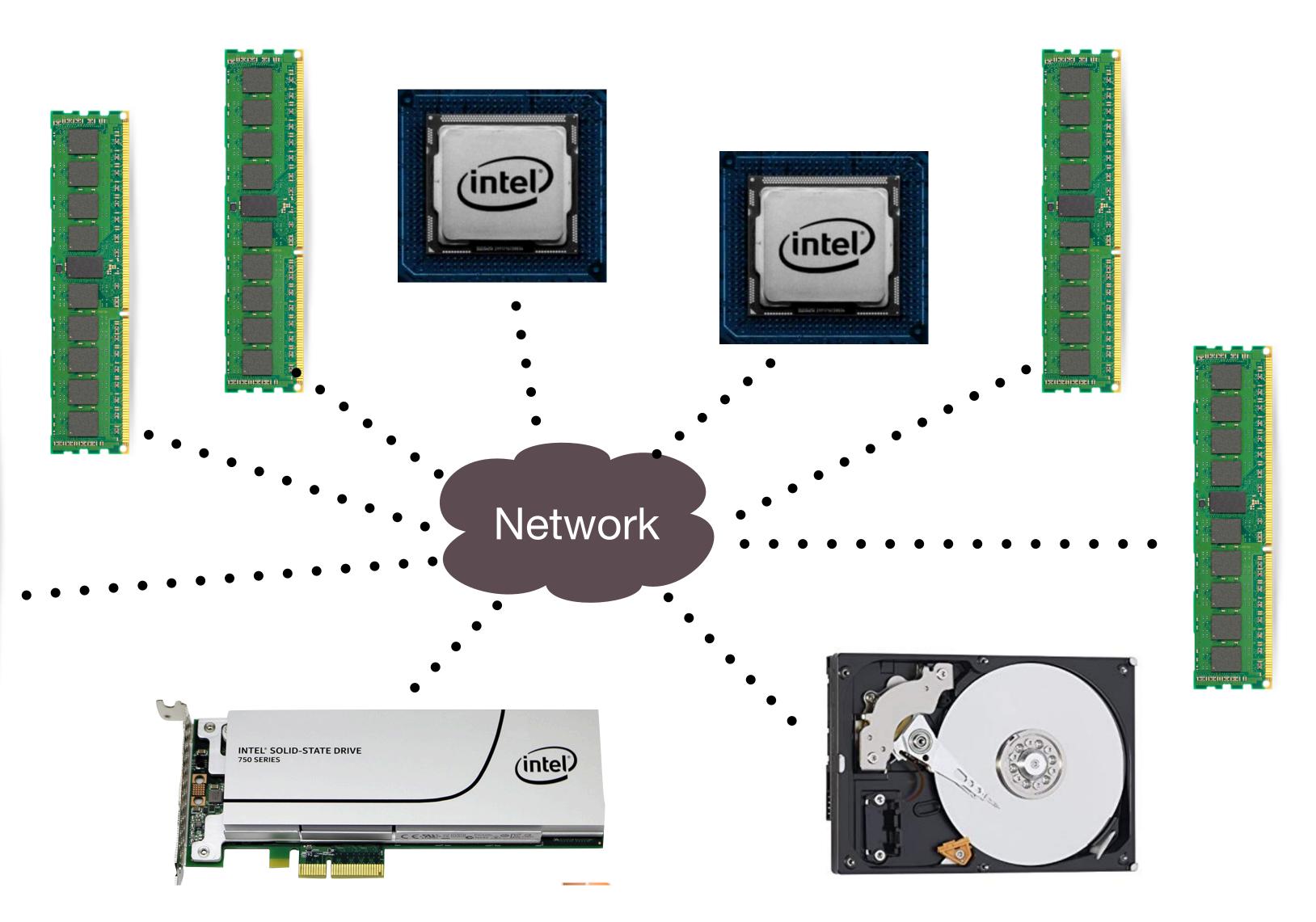

### Hardware Resource Disaggregation:

# Breaking monolithic servers into distributed, network-attached hardware components

# Workshop on Resource Disaggregation and Serverless (WORDS 2022)

- Website: https://www.wordsworkshop.org/

- Submission deadline: 9/29/2022

- Workshop date: 11/17/2022 (virtual or hybrid)

- Types of papers

- Vision paper, completed new work (up to 5 pages)

- published work (2 page abstract)

- PC chairs

- Arvind Krishnamurthy, University of Washington

- Yiying Zhang, University of California San Diego

## **Existing Disaggregated Memory Systems**

- LegoOS [OSDI '18]

- FastSwap [EuroSys '20]

- AIFM [OSDI '20]

- Semeru [OSDI '20]

####

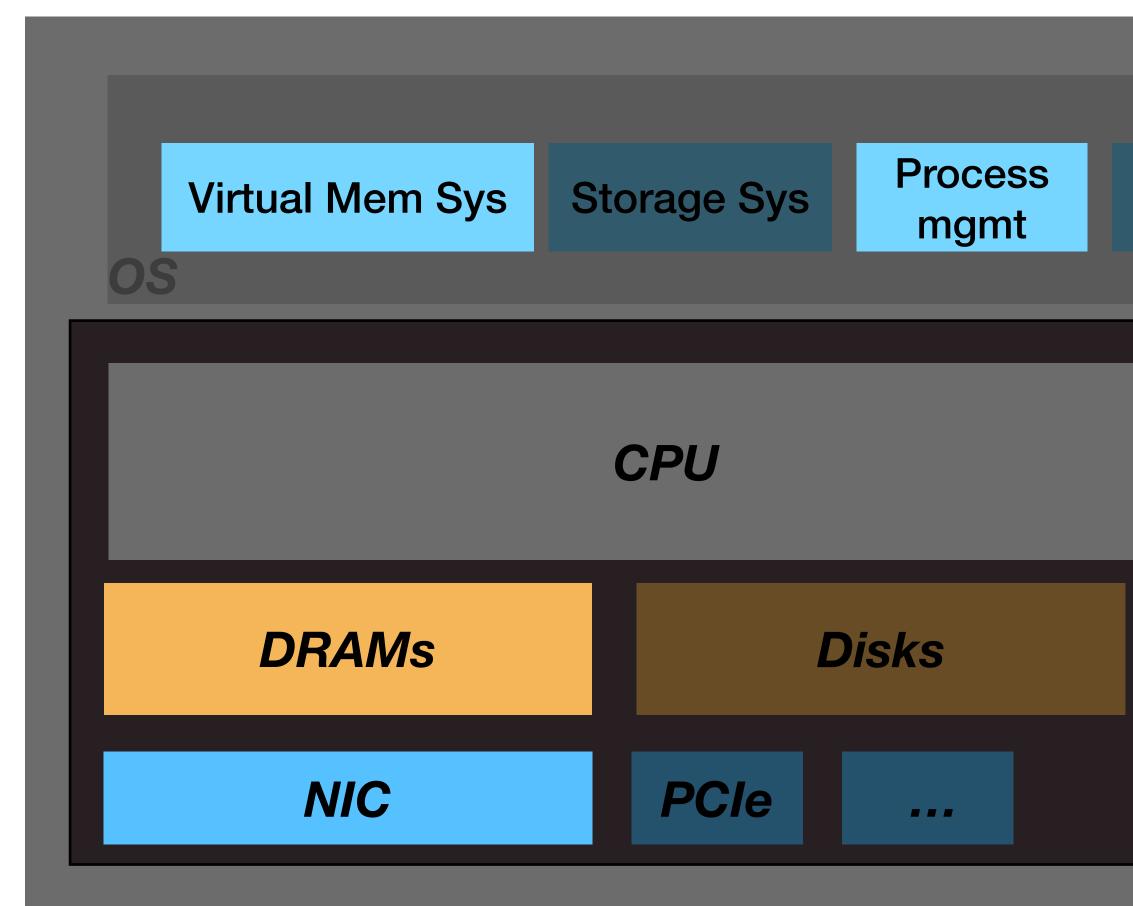

#### All existing works use server to Build/Emulate disaggregated memory devices

#### 5.1 Implementation

We implemented Kona as a C library that interposes on an application's memory allocation and uses a cooperative user thread for

handling page faults [80]. T 5.1 Hardware Emulation Emulating hardware sur

(LoC). The Kona server an Since there is no real resource disaggregation hardware, and were implemented in 5 w Emulate aggregated hardware components using commonly servers by limiting their internal hardware usages. For example, to emulate controllers for mComponents and sComponents, we limit the usable cores of a server to two. To emulate pComponents, we limit the amount of usable main memory of a server and configure it as LegoOS software-managed ExCache.

# How about real hardware?

- Introduction

- Motivation: Why do we need real hardware?

- Clio Overview: Interface and overall approach

- Design: How we remove "state"

- Implementation and evaluation results

#### Features

- Standalone

- Host memory

- Directly connect to network

- Shared by applications

# **Disaggregated Memory Hardware**

# **Could Server Emulation work?**

. . .

#### Memory Node (Server)

# Servers are overkill for memory disaggregation.

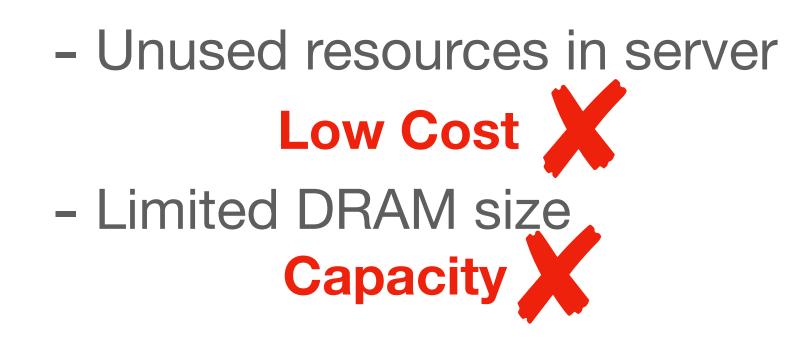

# Could RDMA work?

16.8ms!

#### CXL?

Need specialized interconnect Not immediately available

-Limited NIC cache of OS management structures Scalability

-Slow page fault operations in data path Tail Latency Page Fault

**RDMA** is not designed for standalone memory disaggregation

11

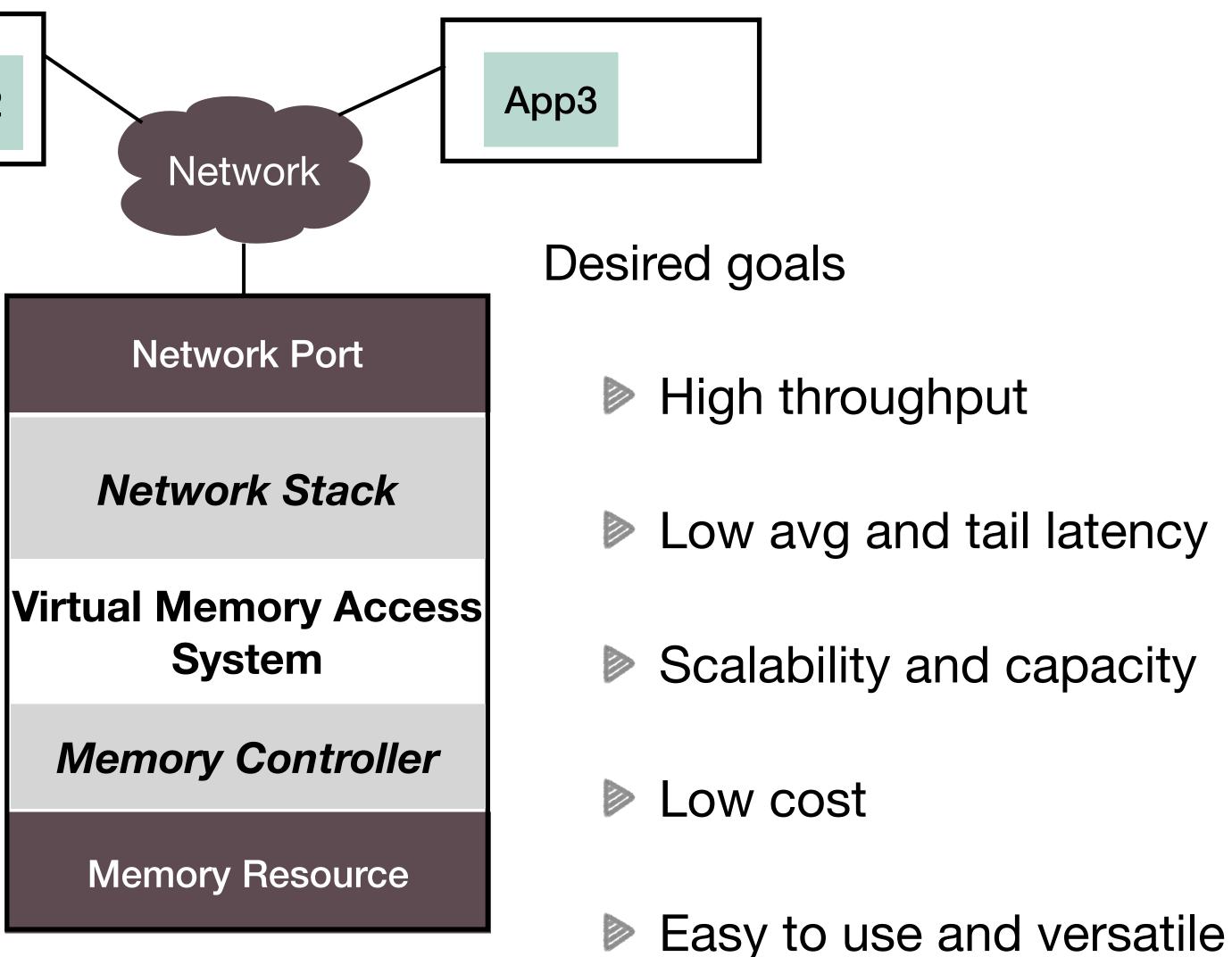

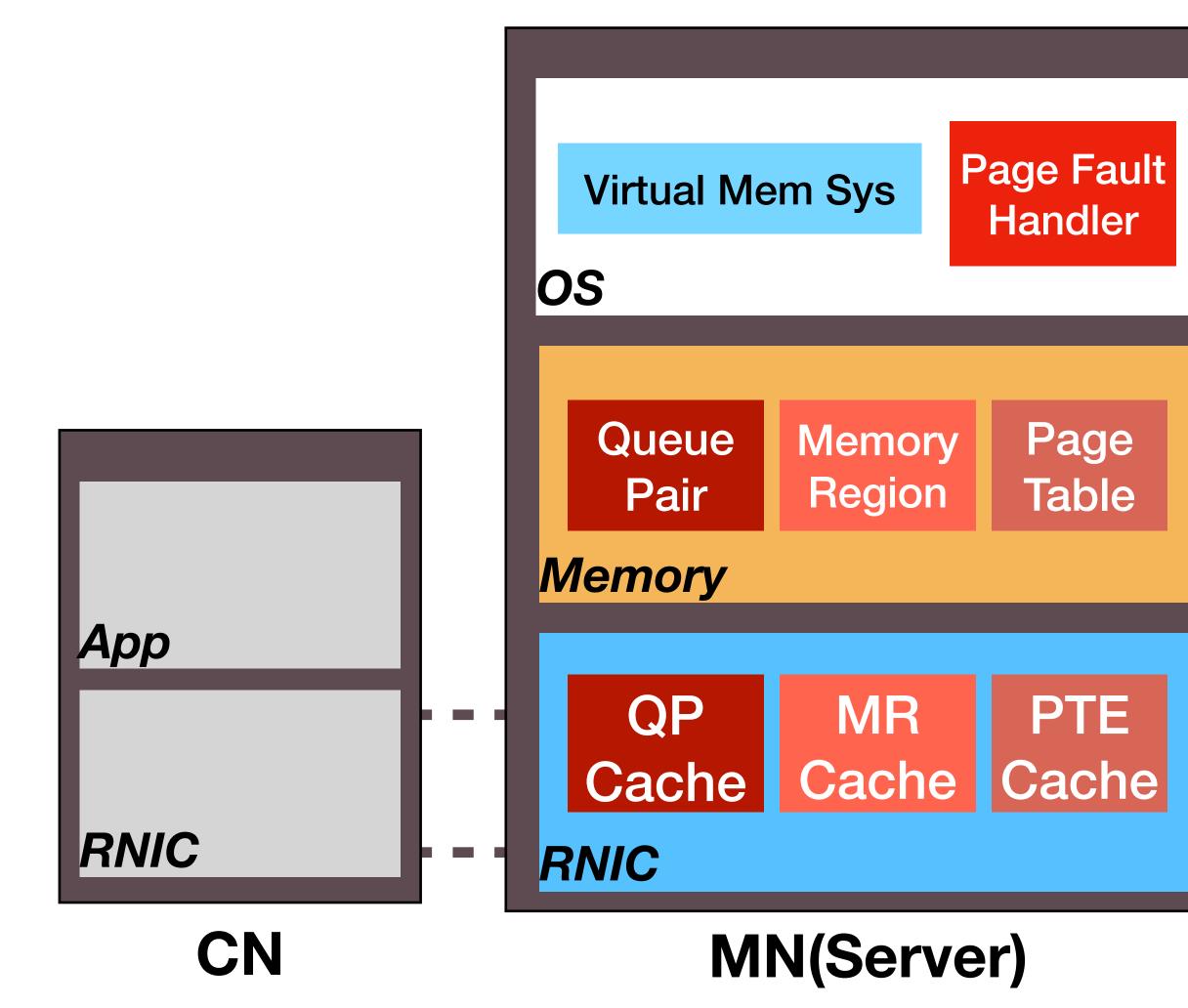

# What we build: Clio [ASPLOS'22]

a hardware-based disaggregated memory system that virtualizes, protects, and manages disaggregated memory at standalone memory nodes

- Introduction

- Motivation: Why we need real hardware

- Clio Overview: Interface and overall approach

- Design: How we remove "state"

- Implementation and evaluation results

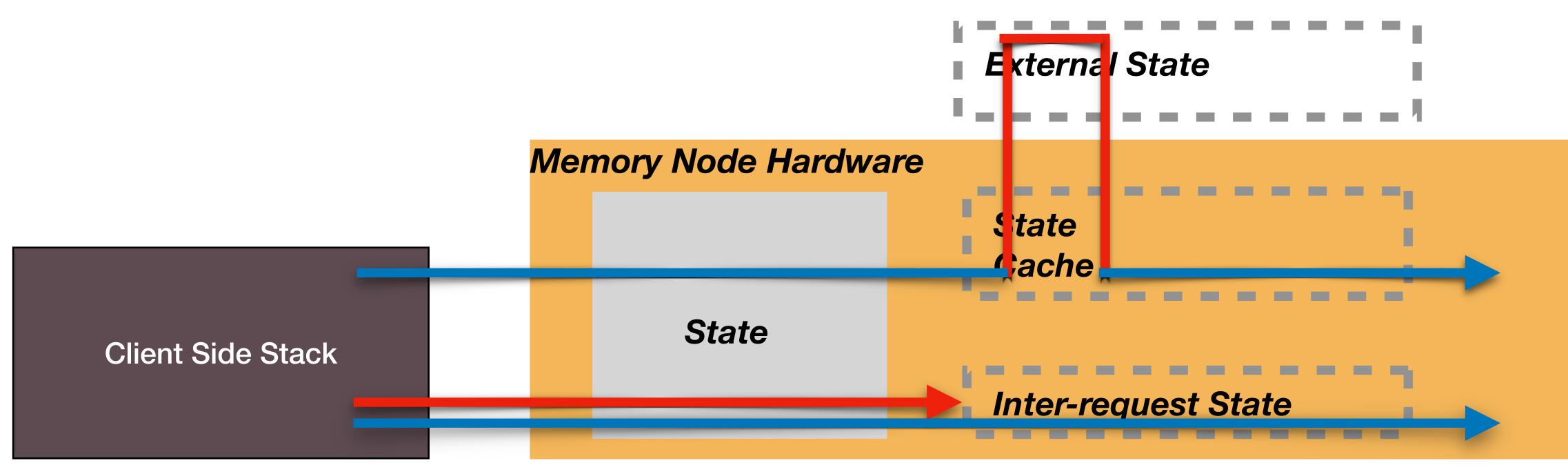

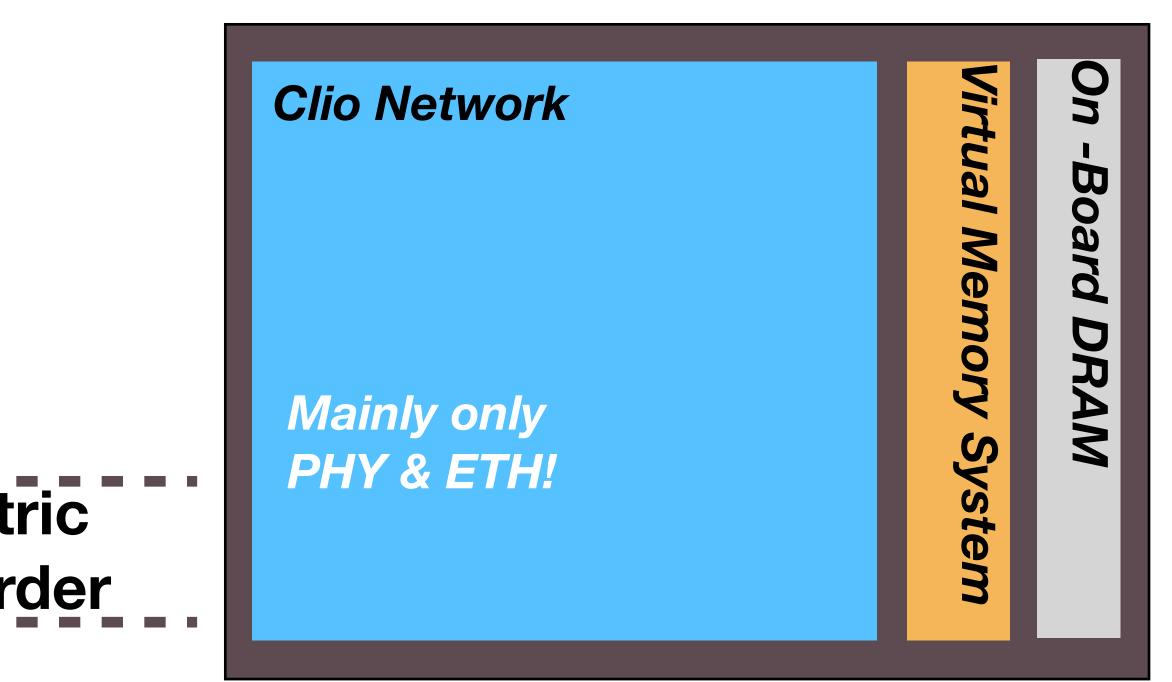

# Main Idea Eliminate state from hardware

"state": Metadata stored on the memory node that need to be accessed or updated when processing requests.

# **Benefit of Removing State**

#### **Compute Node**

- Avoiding inter-request state can make the pipeline smooth

#### **Memory Node**

Minimizing state can reduce cost, reduce tail latency, and improve scalability

- Introduction

- Motivation: Why we need real hardware

- Clio Overview: Interface and overall approach

- Design: How we remove "state"

- Implementation and evaluation results

### How to eliminate state from MN hardware

- 1. Reduce state in disaggregated memory protocol

- 2. Move state to compute node

- 3. Remove state from critical path

- 4. Optimize hard-to-remove state to bounded size

**Overall Approach: Co-designing hardware, network, and software**

### How to eliminate state from MN hardware

- 1. Reduce state in disaggregated memory protocol

- 2. Move state to compute node

- 3. Remove state from critical path

- 4. Optimize hard-to-remove state to bounded size

**Overall Approach: Co-designing hardware, network and software**

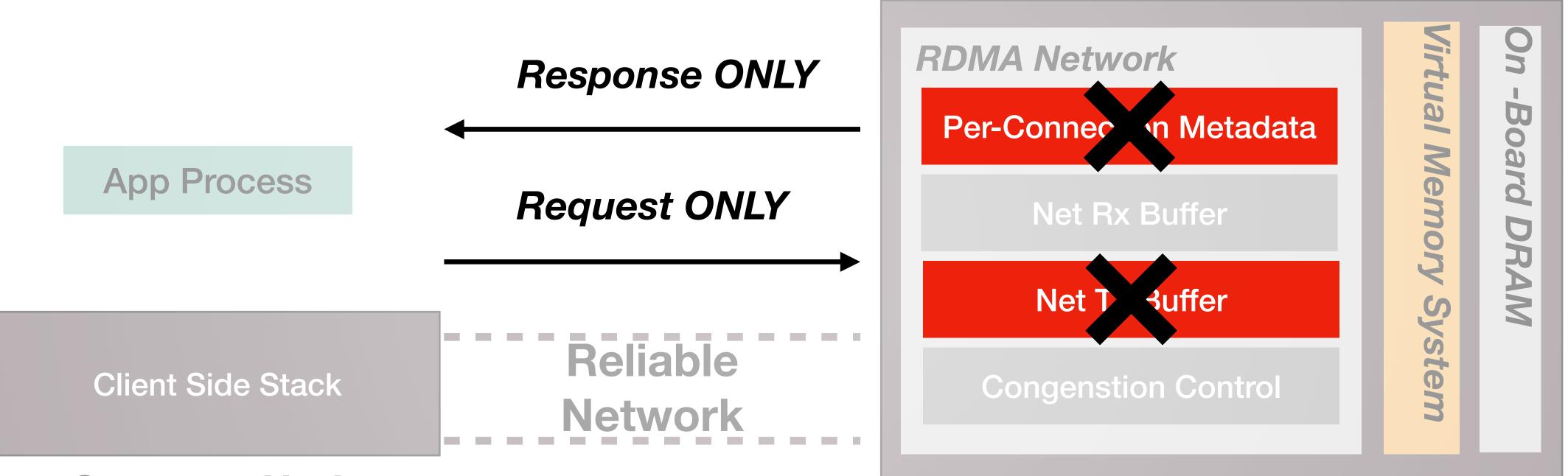

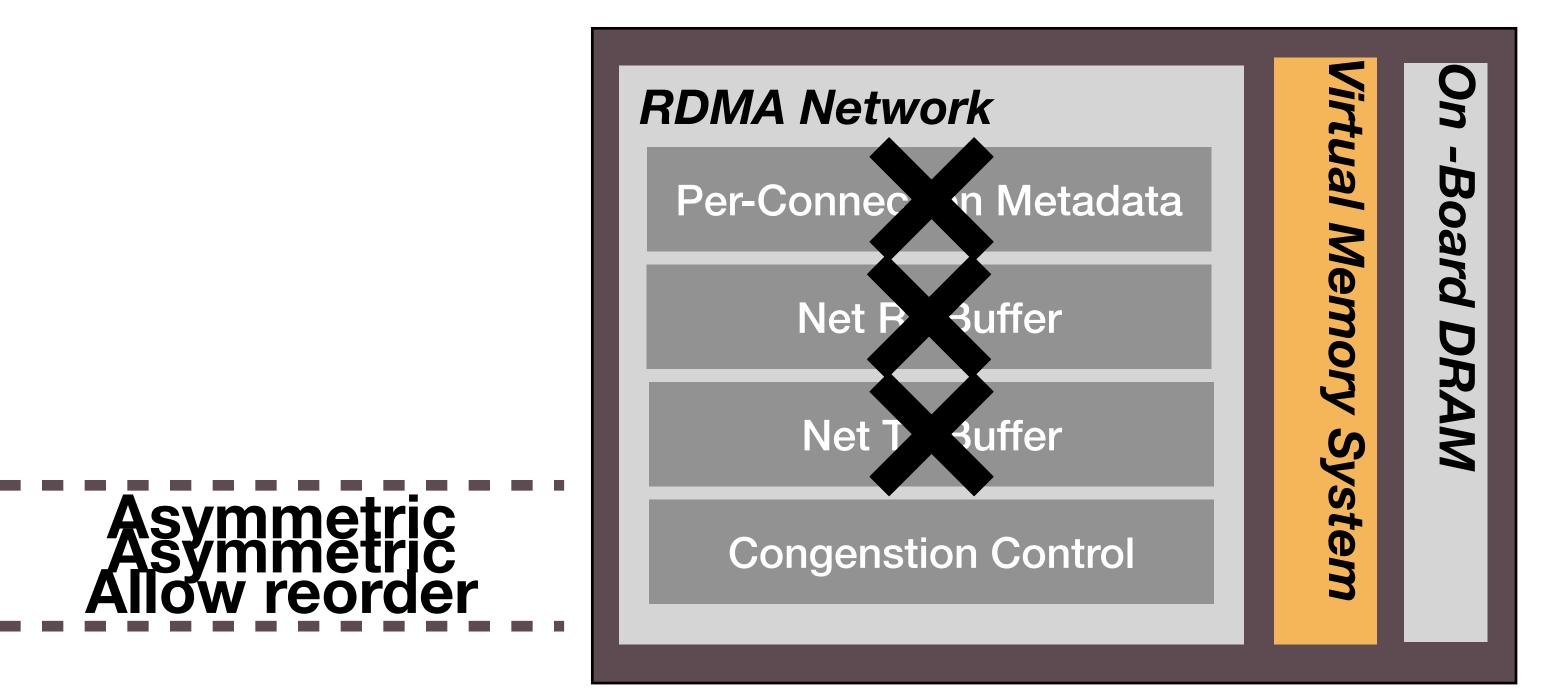

### Reduce state in disaggregated memory protocol > **Asymmetric Memory Request Protocol**

#### **Compute Node**

#### **Memory Node**

• **Observation:** accesses to MNs are always in the request-response style

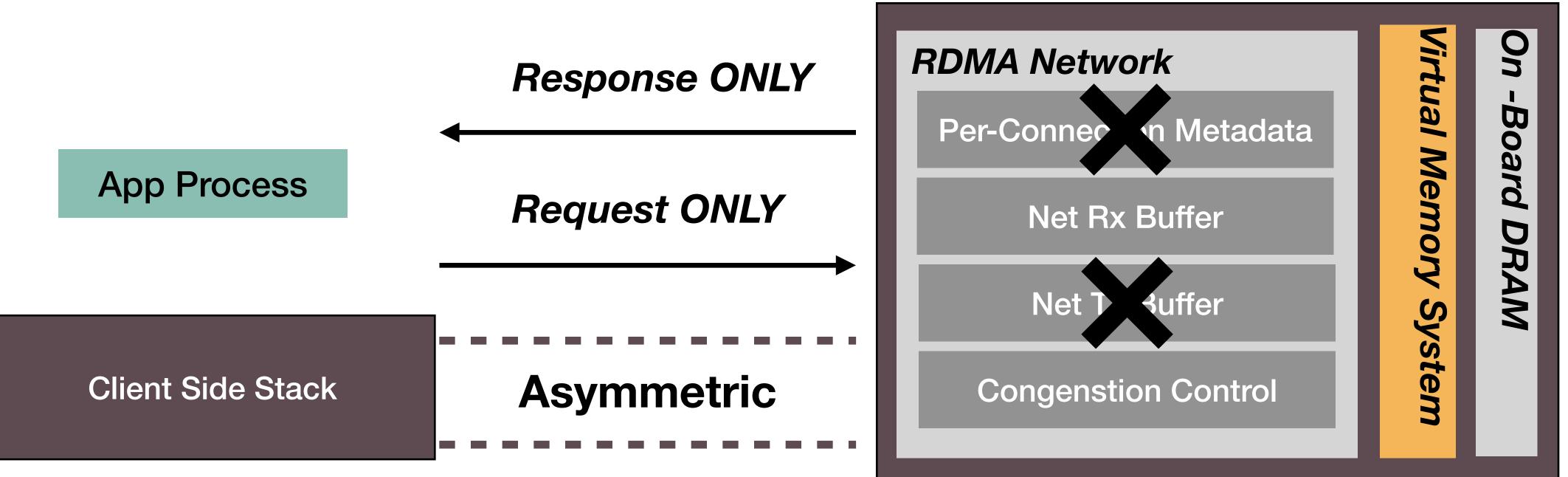

### Reduce state in disaggregated memory protocol > **Asymmetric Memory Request Protocol**

#### **Compute Node**

• **Observation:** accesses to MNs are always in the request-response style **Asymmetric RPC-style, connection-less network protocol**

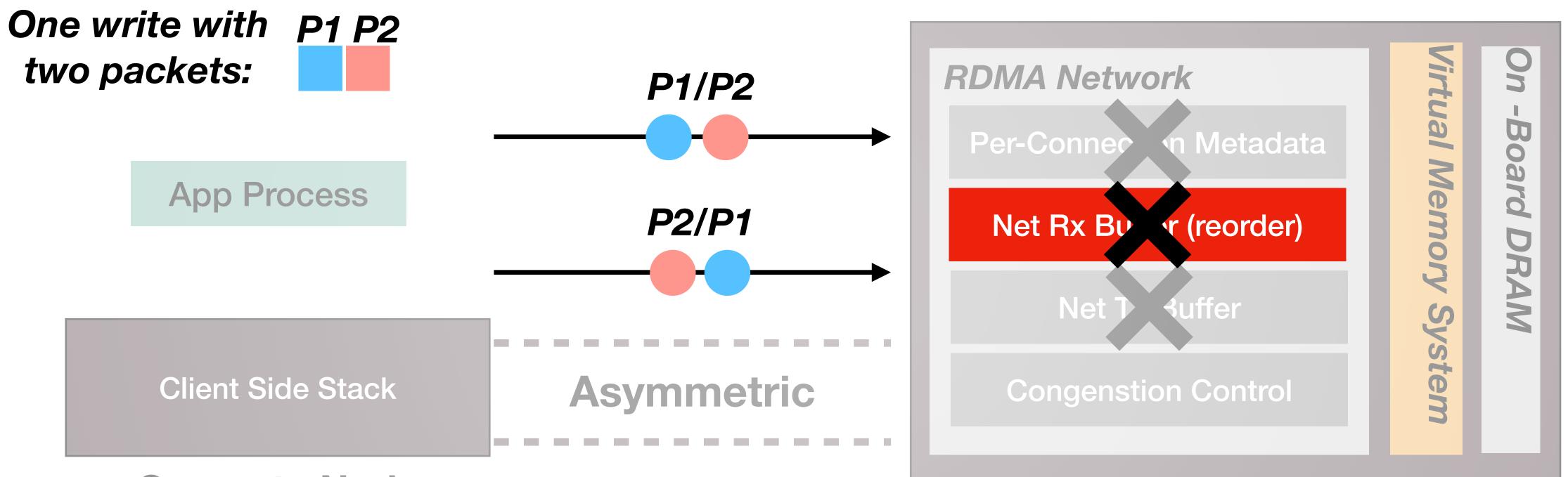

#### Reduce state in disaggregated memory protocol > **Network Ordering**

**Compute Node**

#### **Memory Node**

#### Observation: Memory requests can tolerate certain network reordering

#### Reduce state in disaggregated memory protocol > **Network Ordering**

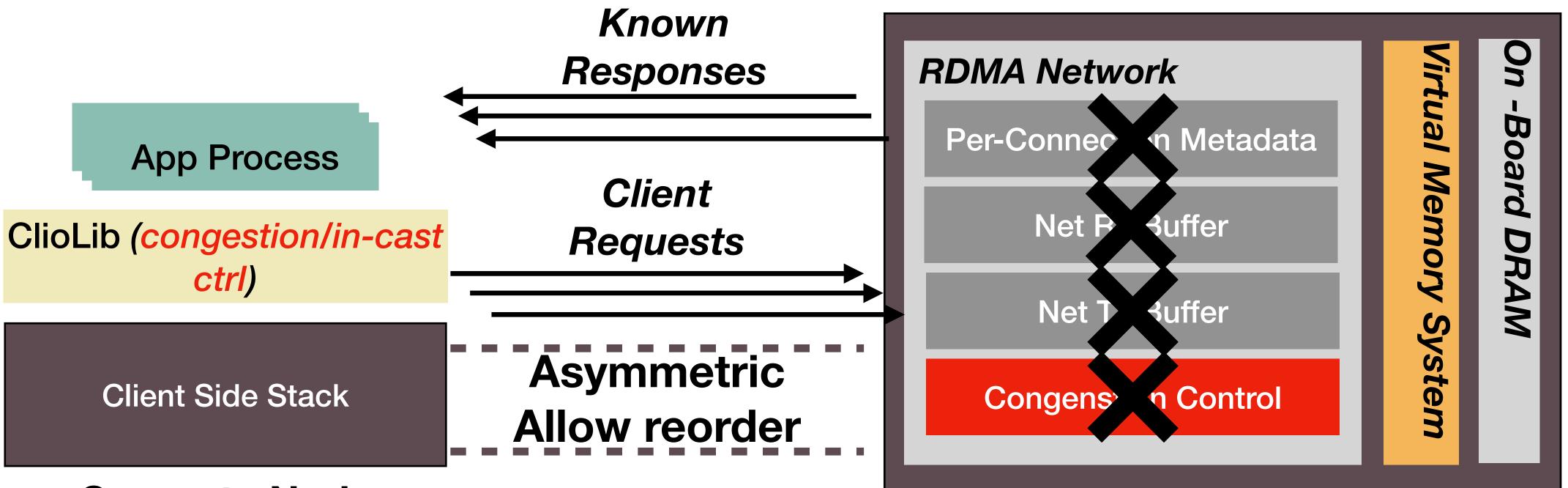

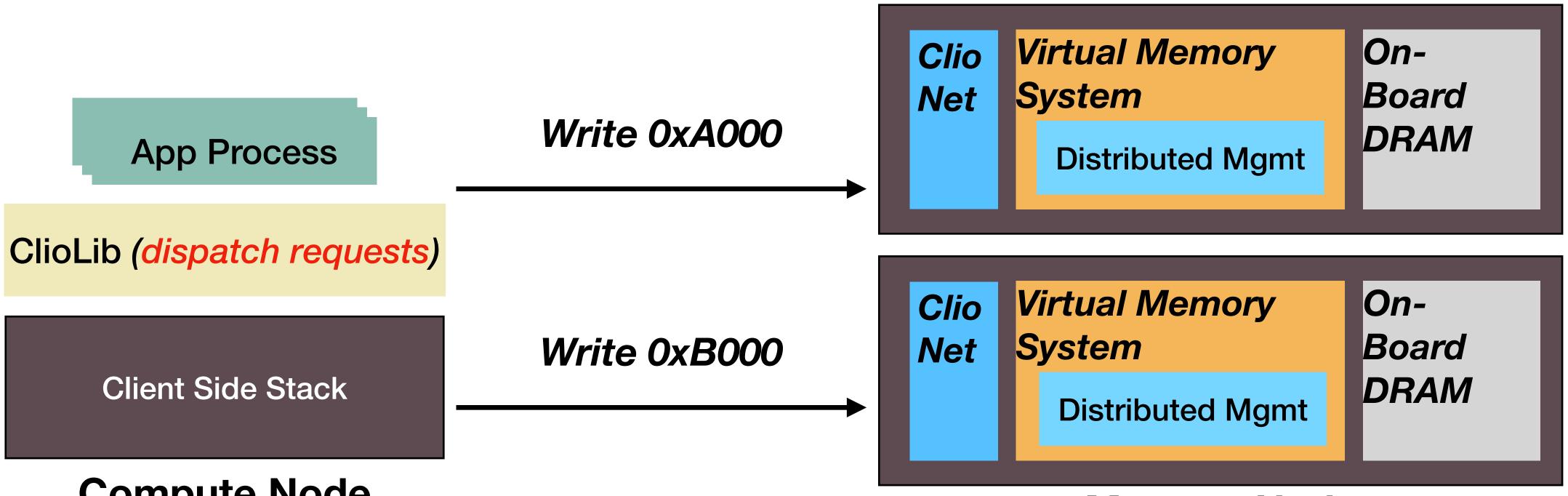

**App Process**

**Client Side Stack**

**Compute Node**

**Release networking ordering requirements**

#### **Memory Node**

Observation: Memory requests can tolerate certain network reordering

### How to eliminate state from MN hardware

- 1. Reduce state in system protocol

- 2. Move state to compute node

- 3. Remove state from critical path

- 4. Optimize hard-to-remove state to bounded size

### Move state to Compute Node > **Congestion and Flow Control**

#### **Compute Node**

Observation: CN knows the size of both requests and responses Move congestion and in-cast control to CN side

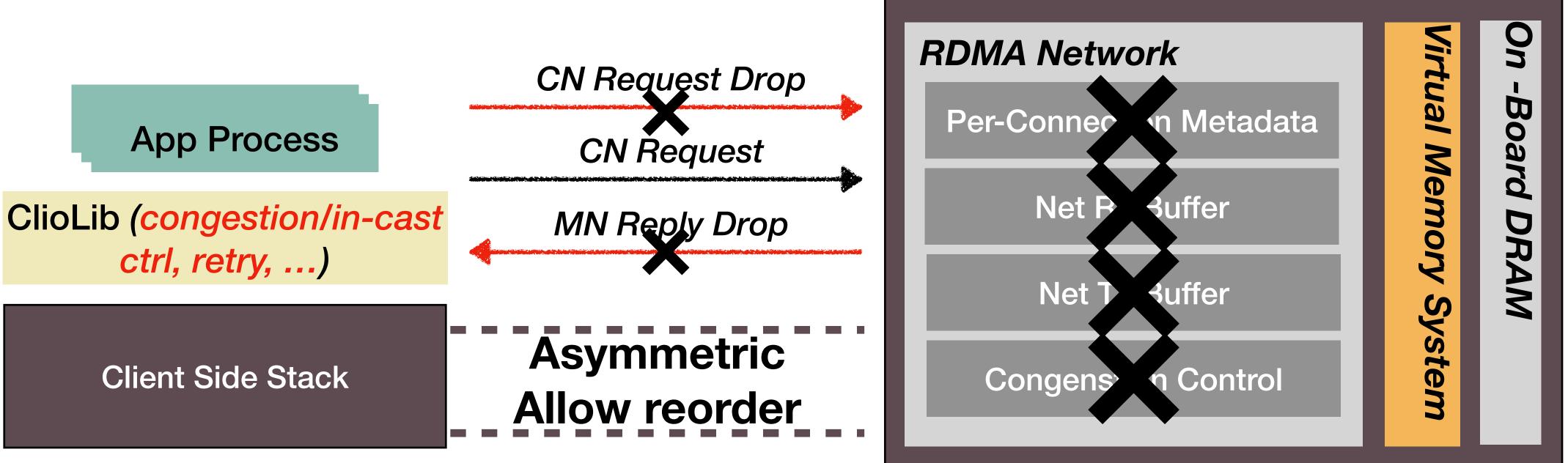

### Move state to Compute Node > Handle Retry

#### **Compute Node**

Observation: Network losses are rare and fully observed by CN Let CN side software handling retry

### Move state to Compute Node > Handle Retry

ClioLib (congestion/in-cast ctrl, retry, ...)

ETH & PHY

Asymmetric Allow reorder

#### **Compute Node**

### How to eliminate state from MN hardware

- 1. Reduce state in system protocol

- 2. Move state to compute node

- 3. Remove state from critical path

- 4. Optimize hard-to-remove state to bounded size

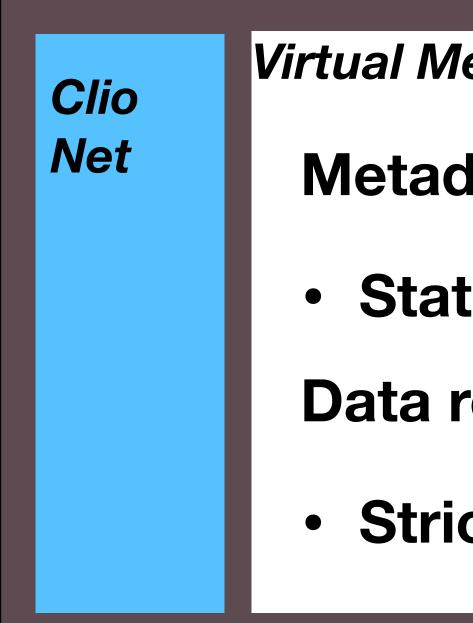

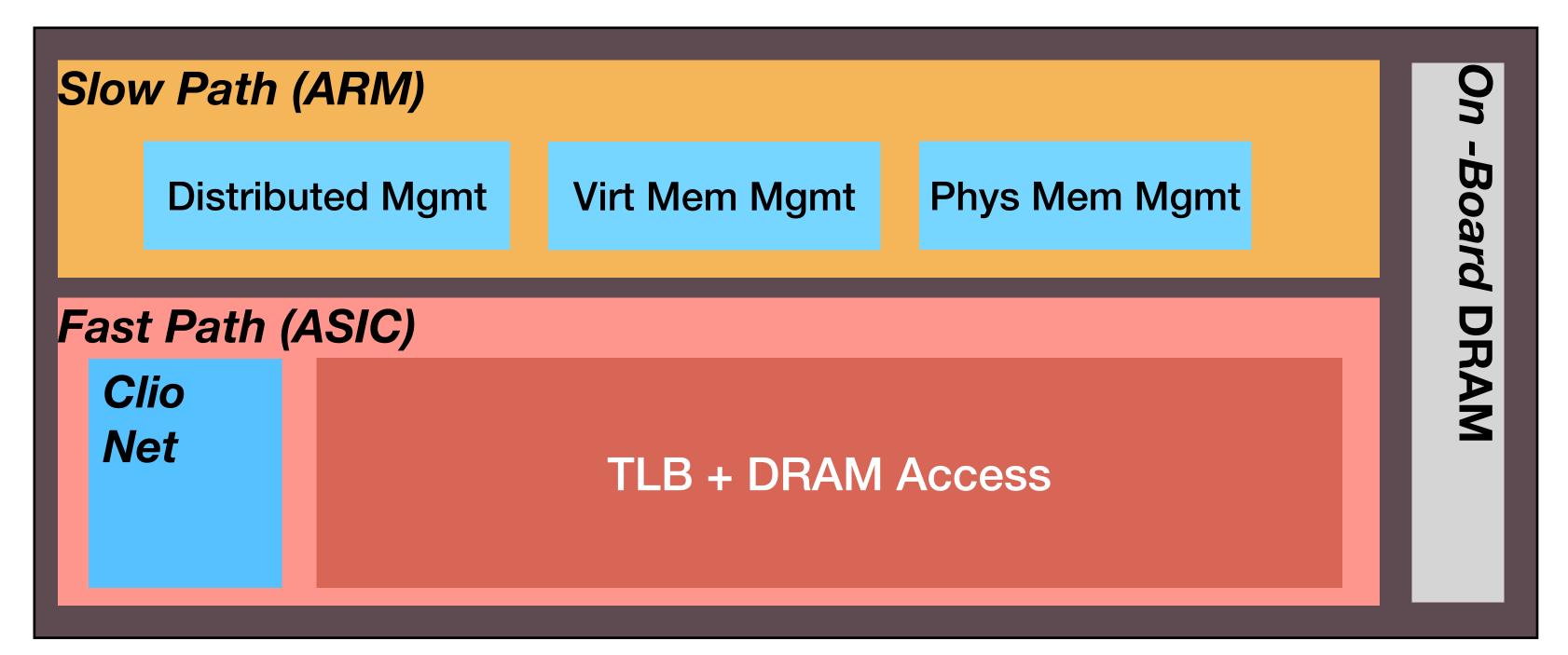

### Remove state from critical path > Splitting Fast Path and Slow Path

#### remote\_alloc(pid, size) read/write (pid, va)

Observation: Metadata and data requests have different state and performance requirements

- Virtual Memory System

- Metadata requests

- Stateful, flexible, less strict latency

- **Data requests (Performance critical!)**

- Strict latency and throughput

#### **Memory Node**

0n

-Board DRAM

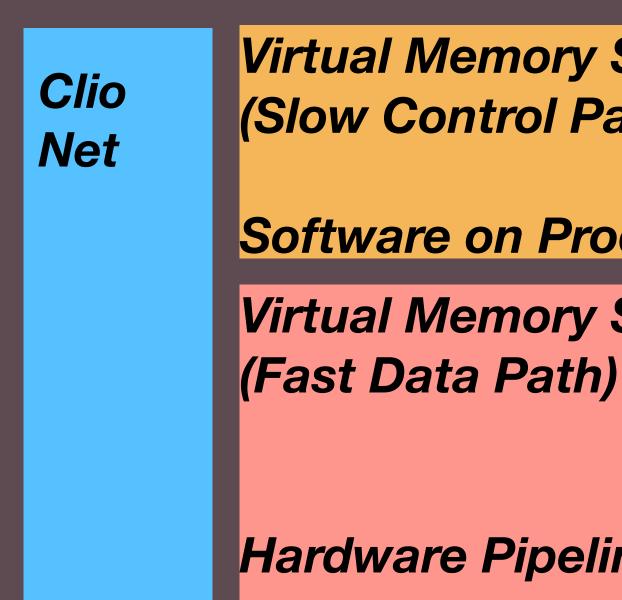

### Remove state from critical path > **Splitting Fast Path and Slow Path**

#### remote\_alloc(pid, size) read/write (pid, va)

#### Splitting virtual memory system into fast path and slow path

Virtual Memory System (Slow Control Path)

Software on Processor

Virtual Memory System

Hardware Pipeline on ASIC

#### **Memory Node**

0n

-Board

DRAM

### Remove state from critical path > **Splitting Fast Path and Slow Path**

#### remote\_alloc(pid, size) read/write (pid, va)

#### **Memory Node**

Solution: Splitting virtual memory system into fast path and slow path

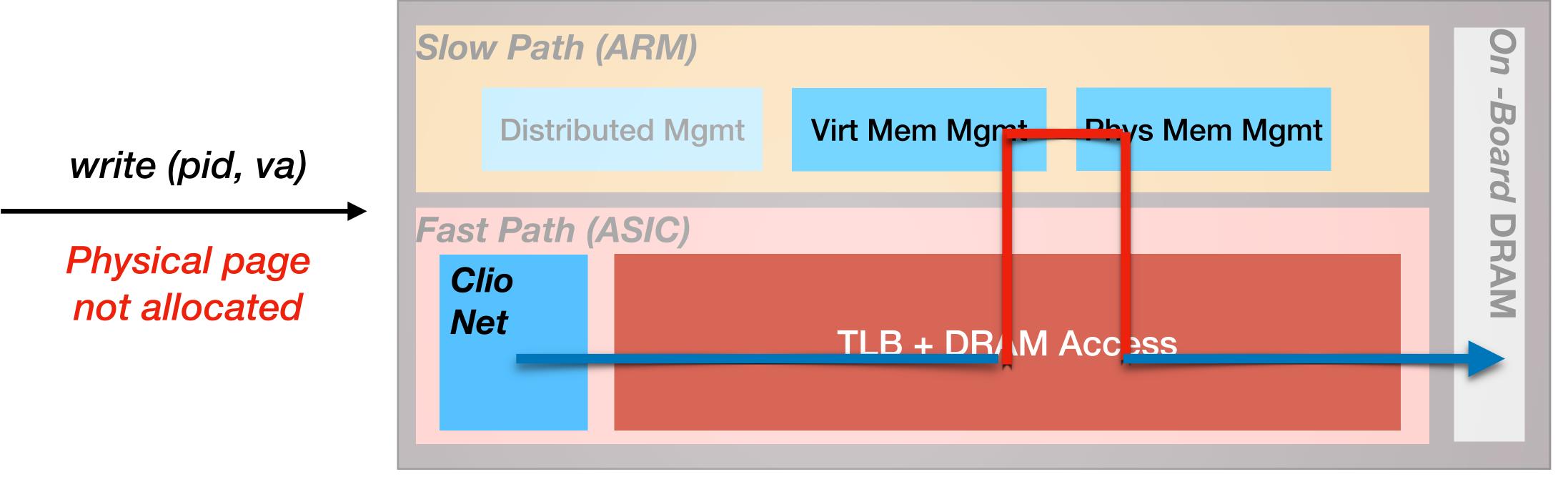

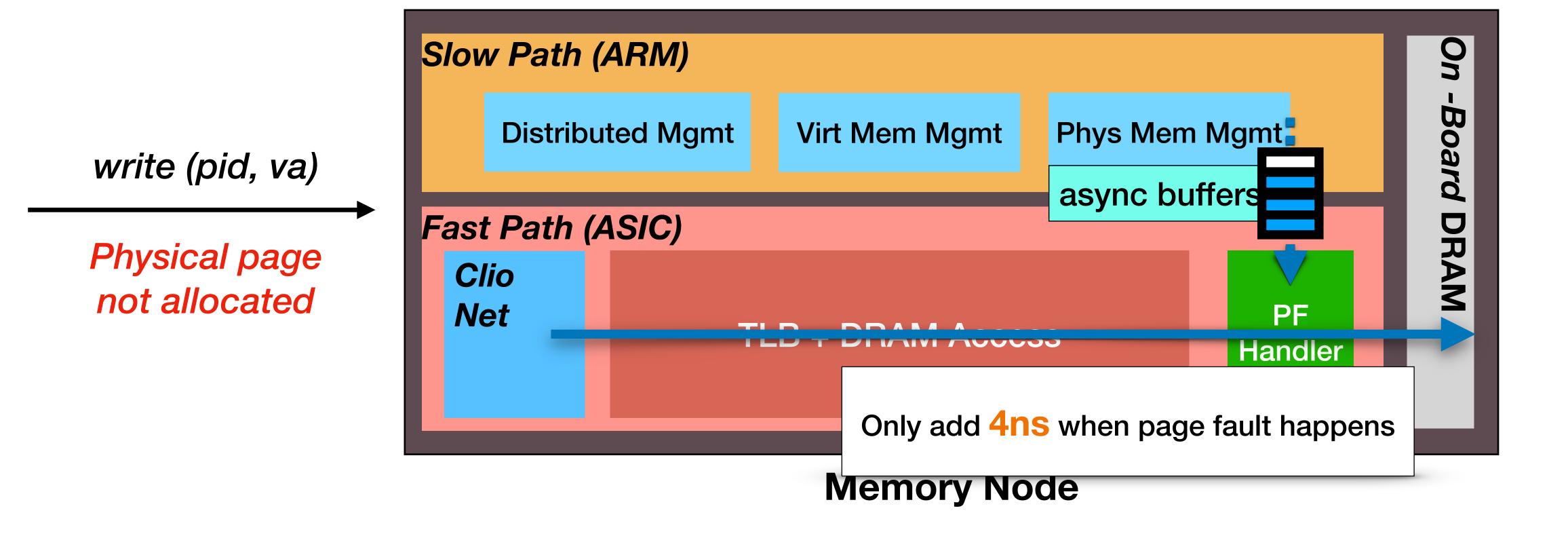

### Remove state from critical path > Handling Page Fault

#### **Memory Node**

Observation: Access requests with pagefault need stateful allocation operations

### Remove state from critical path > Handling Page Fault

#### <u>Spervation: Access requests with page apply seed stateful allocation operations</u>

### How to eliminate state from MN hardware

- 1. Reduce state in system protocol

- 2. Move state to compute node

- 3. Remove state from critical path

- 4. Optimize hard-to-remove state to bounded size

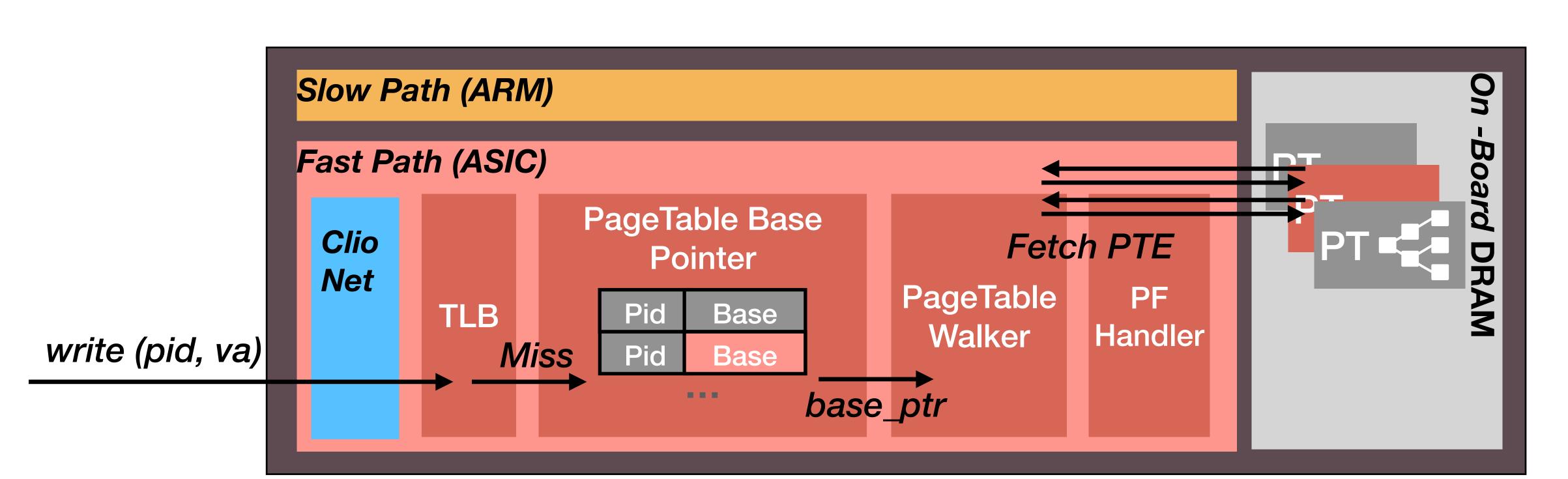

### Optimize state to bundled size > **Traditional Page Table Design (Strawman)**

**Observation: Size of base pointer table and page tables grow with**

number of clients, needs multiple DRAM accesses to walk page tables

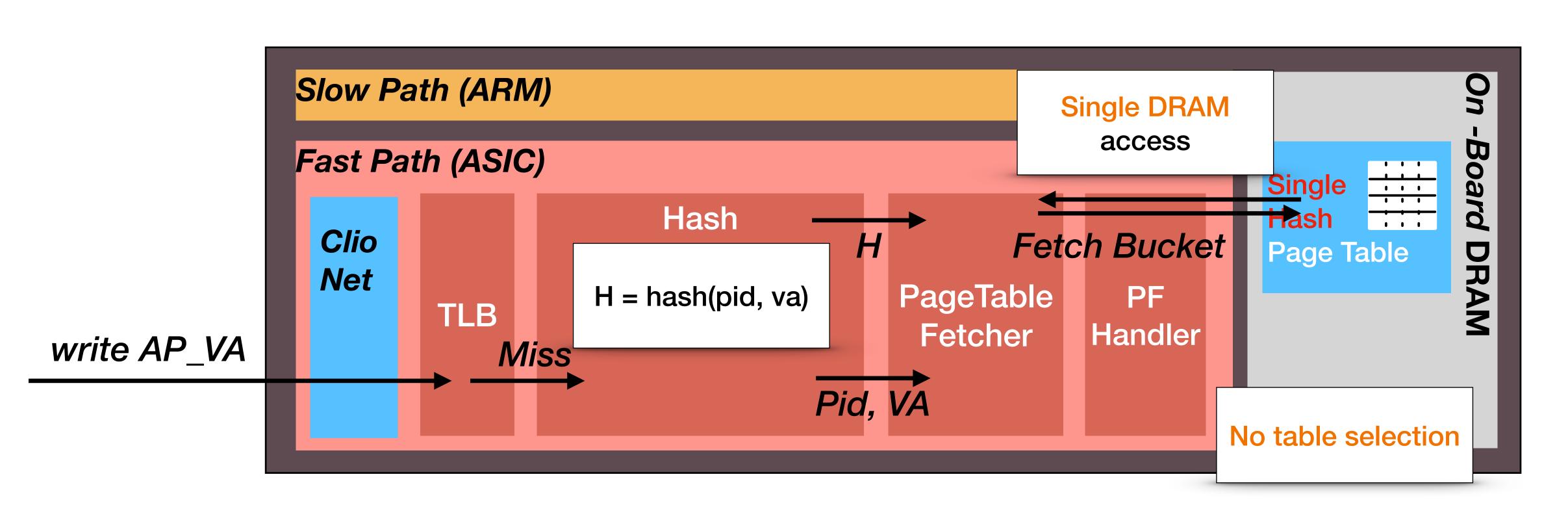

### Optimize state to bundled size > Hash-Based Page Table

Hash Page Table for **bounded size** and **access time (single DRAM access)**

### "eliminate state" summary

- Reduce state in system protocol: Disaggregated protocol, consistency model, ...

- Move state to compute node: Congestion control, retry, dependency check, ...

- Remove state from critical path: Hardware pagefault, memory region, ...

- Optimize state to bounded size: Hash-based pagetable, atomic operations, ...

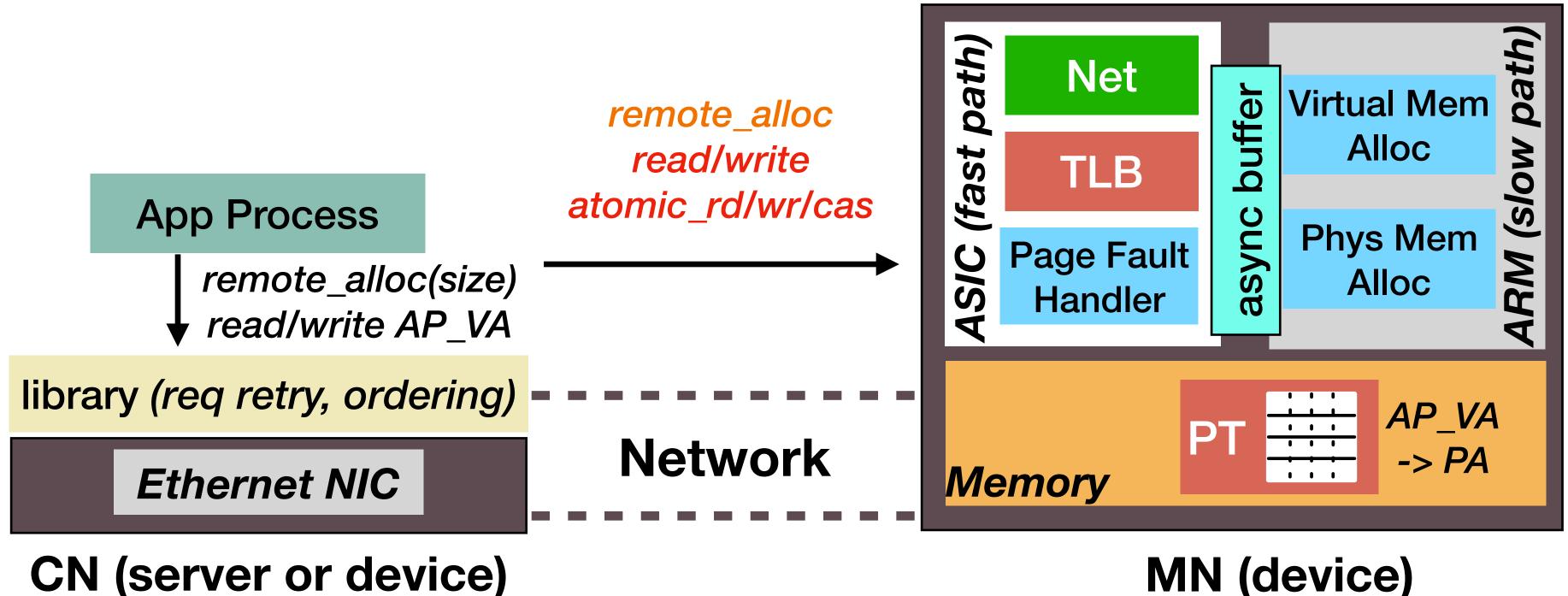

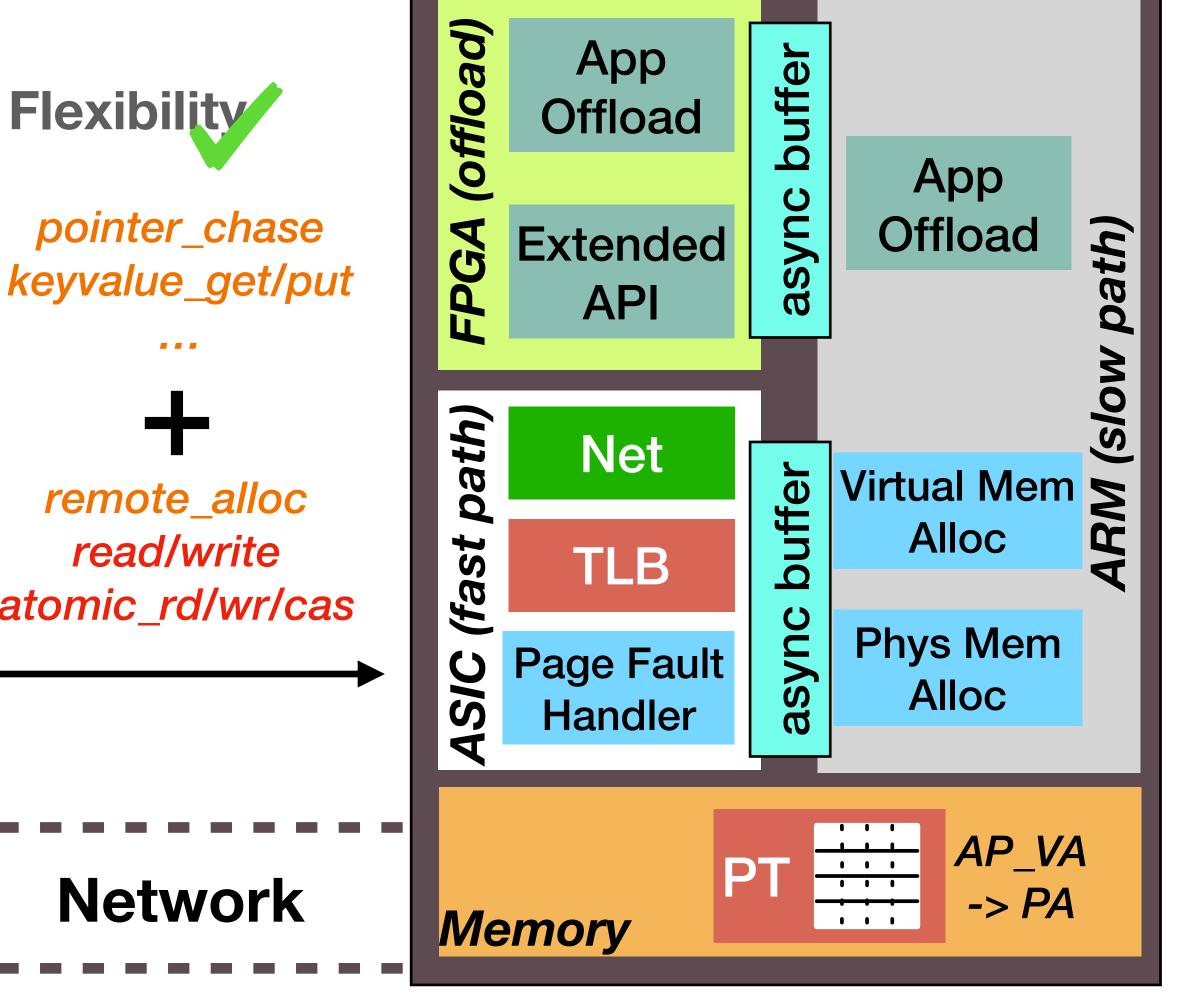

### Extend computation offloading

#### **MN (device)**

## Extend computation offloading

Flexibility

|                                                | App Process  |  | remote<br>read/<br>atomic_r |

|------------------------------------------------|--------------|--|-----------------------------|

| <pre>remote_alloc(size) read/write AP_VA</pre> |              |  |                             |

| library (req retry, ordering)                  |              |  |                             |

|                                                | Ethernet NIC |  | Netv                        |

| CN (server or device)                          |              |  |                             |

**MN (device)**

#### **Compute Node**

can span multiple memory nodes.

#### **Memory Nodes**

Multiple Clio boards can form a distributed system, single virtual memory space

- Introduction

- Motivation: Why we need real hardware

- Clio Overview: Interface and overall approach

- Design: How we remove "state"

- Implementation and evaluation results

## Implementation and Application

- Fast path and extended path implemented in hardware using SpinalHDL

- Prototype with Xilinx ZCU106 ARM-FPGA board

- Implemented five applications

- Image compression

- Multi-version object store

- key-value store

- pointer dereferencing

- data analytics operation

#### nented in hardware using SpinalHDL FPGA board

Clio prototype on the Xilinx ZCU106 board

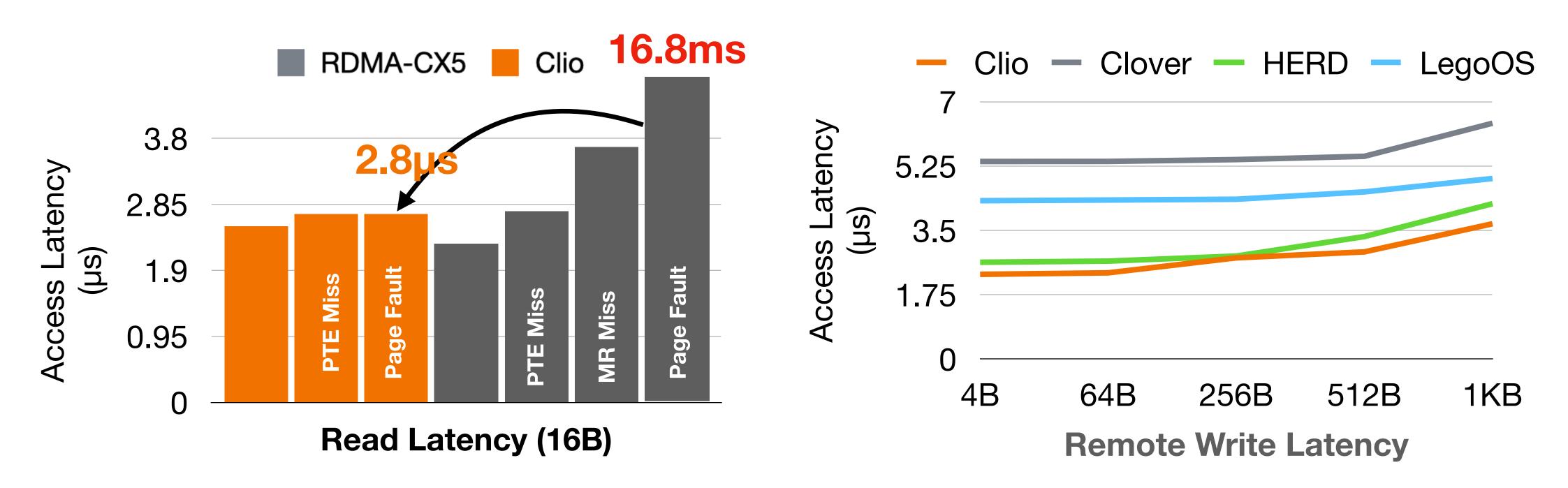

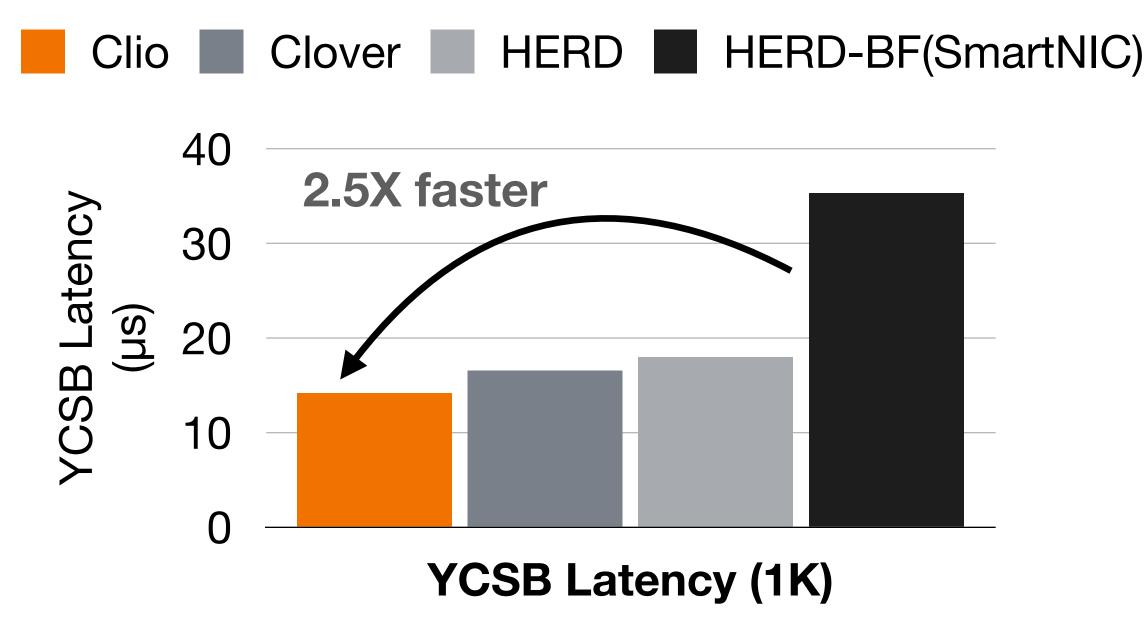

### **Evaluation Results Basic Performance**

- 100Gbps throughput, 2.8µs (avg) 3.2µs (p99) latency

- Orders of magnitude lower tail latency than RDMA

- $\bullet$

# Outperforms Clover [ATC'20], LegoOS [OSDI'18], and HERD [SIGCOMM'14]

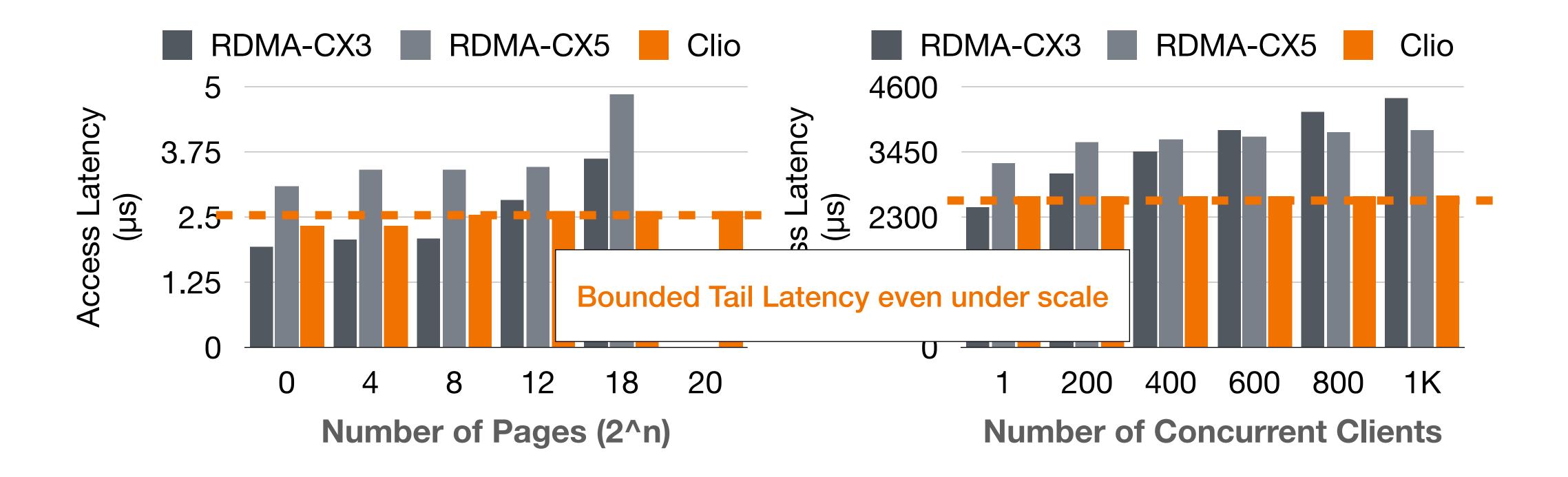

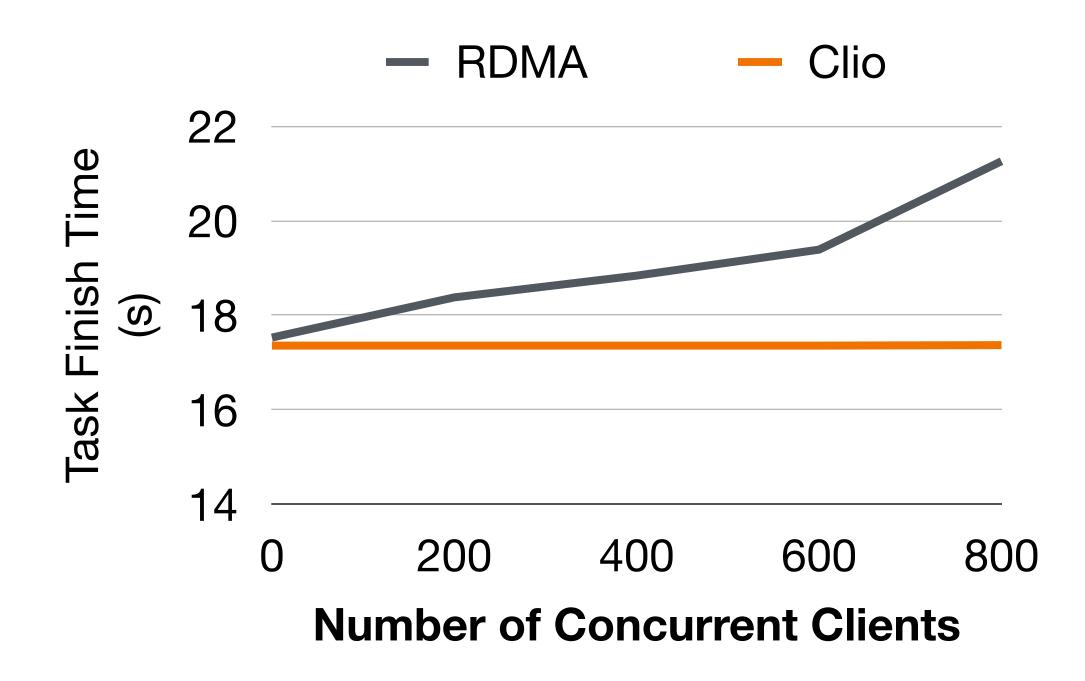

### **Evaluation Results Concurrent Clients and Memory Size**

- **Clio provides bounded access time for data requests**

## Clio scales well with concurrent clients and total memory size

### **Evaluation Results Disaggregated Applications**

- Applications benefits from stable latency and scalability

#### Extended path outperforms CPU based offloading [Herd-BlueField]

### Summary

### Ve built Clio, a real hardwar Achieves all requirement **performance, cost,** s

- We built Clio, a real hardware disaggregated memory system

- Achieves all requirements of memory disaggregation: performance, cost, scalability and flexibility.

- Real benefits of hardware resource disaggregation comes from real hardware

- Building OS functionalities in hardware is feasible but needs new design

- The nature of disaggregation indicates new opportunities and challenges.

- Co-designing software and hardware systems is key in building real hardware.

### Conclusion

**Clio** is a starting point for more real disaggregated hardware

### **Other Recent/Ongoing Disaggregation** Works

- Network disaggregation (hardware implementation)

- Serverless computing on disaggregation

- Secure disaggregation (hardware implementation)

### Thank you! Get Clio at <u>https://github.com/WukLab/Clio</u>